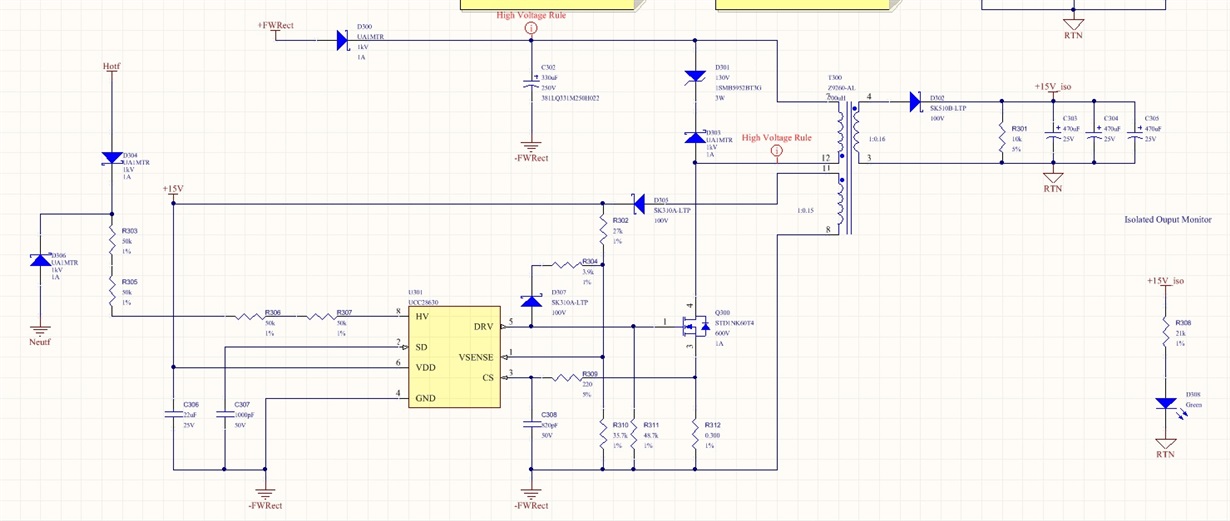

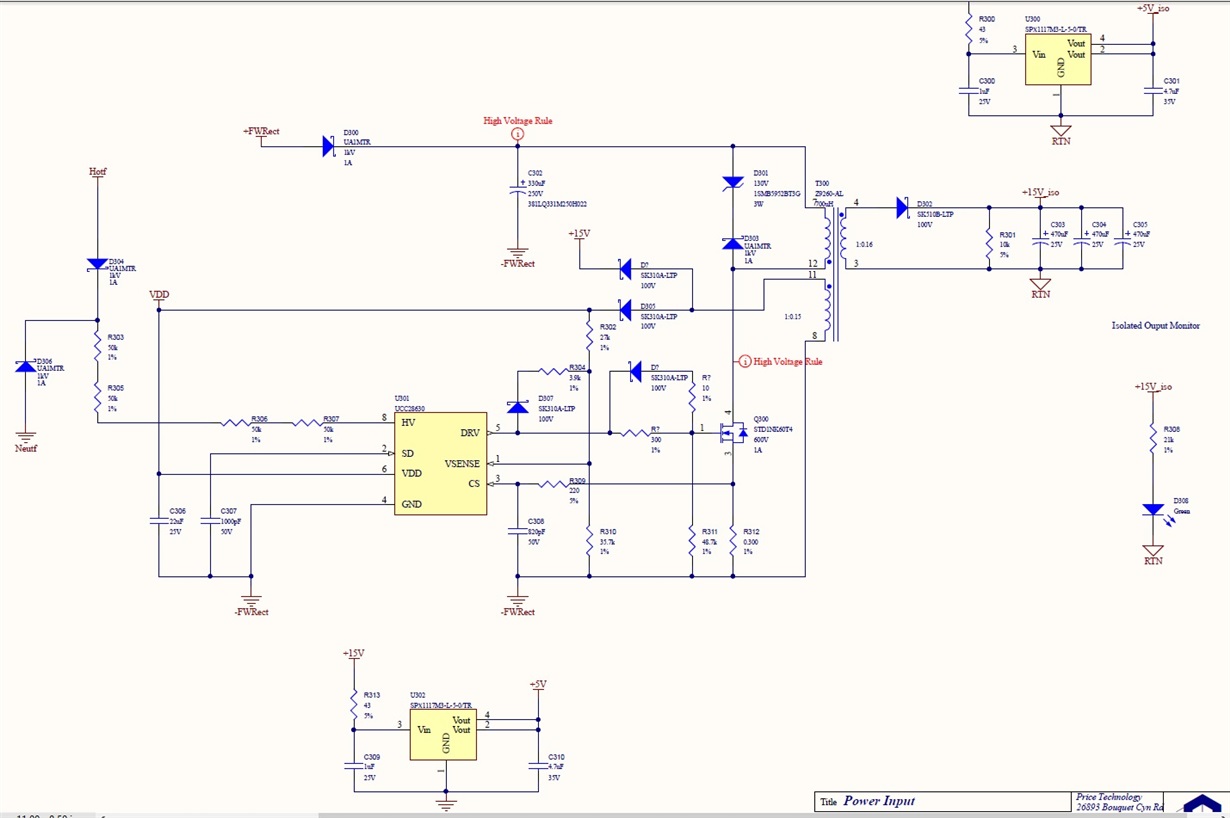

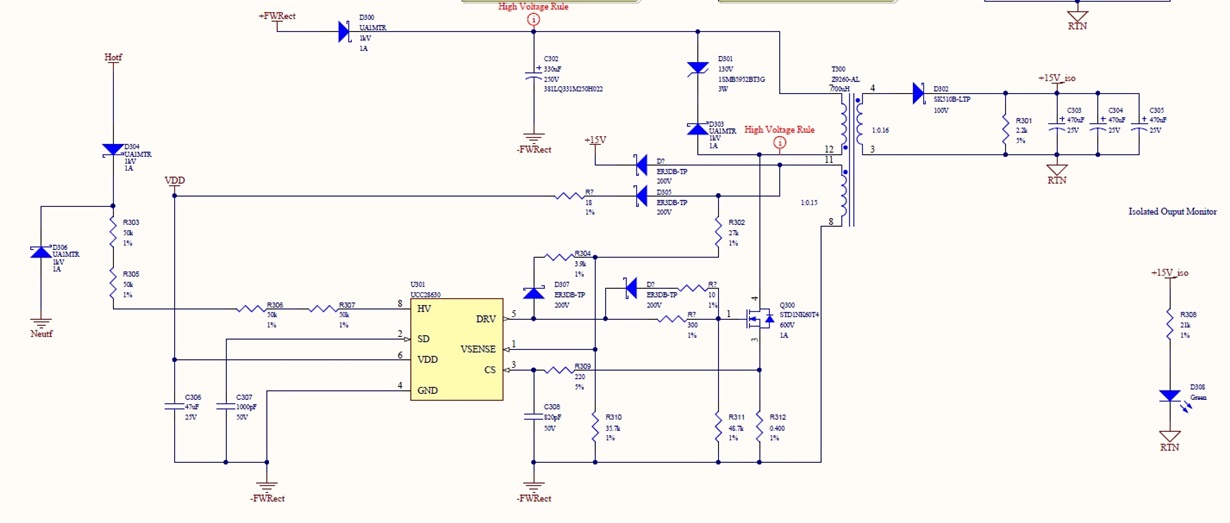

I have powered up a new flyback design using the UCC28630 (Custom design/layout). All models and most of the layout has been verified.

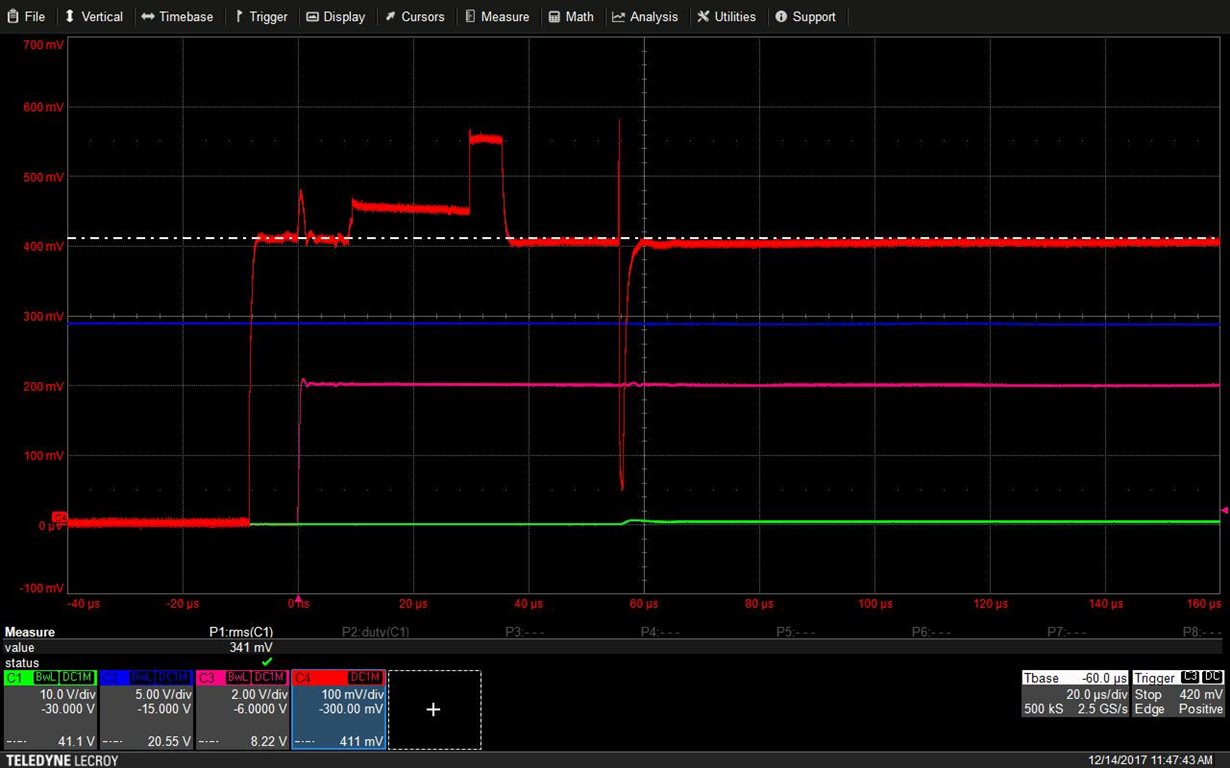

I have been scratching my head over the current issue, since it seems like the circuit should be working; however, when powered on from 120VAC, the VDD pin bounces between 8V-10V as if there is a fault latched on the chip. There is never a DRV PWM voltage and the Vsense pin reads 5.5V at the time of the latched fault. When observing the SD pin, I am seeing a 30us pulse, followed by 21x 1us pulses. This tells me according to other people's post that I have an open or short on Vsense.

I turned the circuit off and removed and tested the resistors and everything tests well as though the fb circuit should be operating normally.

What else could be causing this?

As a side note, the pulse train at VDD never reaches a proper peak voltage. They appear more as low amplitude pulses (0.5V). This circuit also, only has a 10k load populated on the secondary side of the flyback transformer right now. Would this generate issues?

The feedback resistors are 27k, 35.7k with a 0.16 primary to auxiliary turns ratio. I can send a chunk of the schematic if necessary, though I am really just looking for places to hunt.