Hello,

I have some problem with the functionality of UCC27211 gate driver at low temperature (from 10degC downwards).

I wonder if someone from technical support will be able to help me.

The application is a non-isolated buck converter. The UCC27211 is used to drive the conduction mosfet and the synchronous rectifiers.

The driver operates fine at ambient temperature, but when it is tested at 10degC oven temperature or below, the HO and LO stops once every few pulses.

I am able to replicate the problem with several different test units, and I am able to replicate the problem by spraying a pulse of freezer spray over the gate driver instead of testing inside an oven.

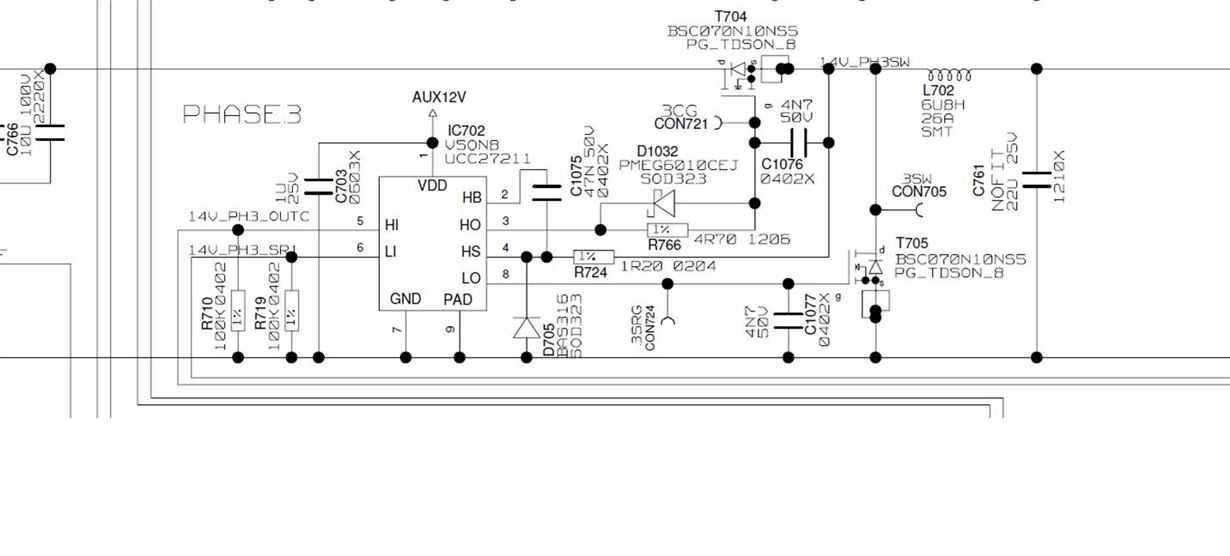

The converter is operating at 200KHz, I have included the relevant part of the schematic below:

Rg-on= R766+R724.

Rg-off= R724. D1032 bypasses R766 during turn off.

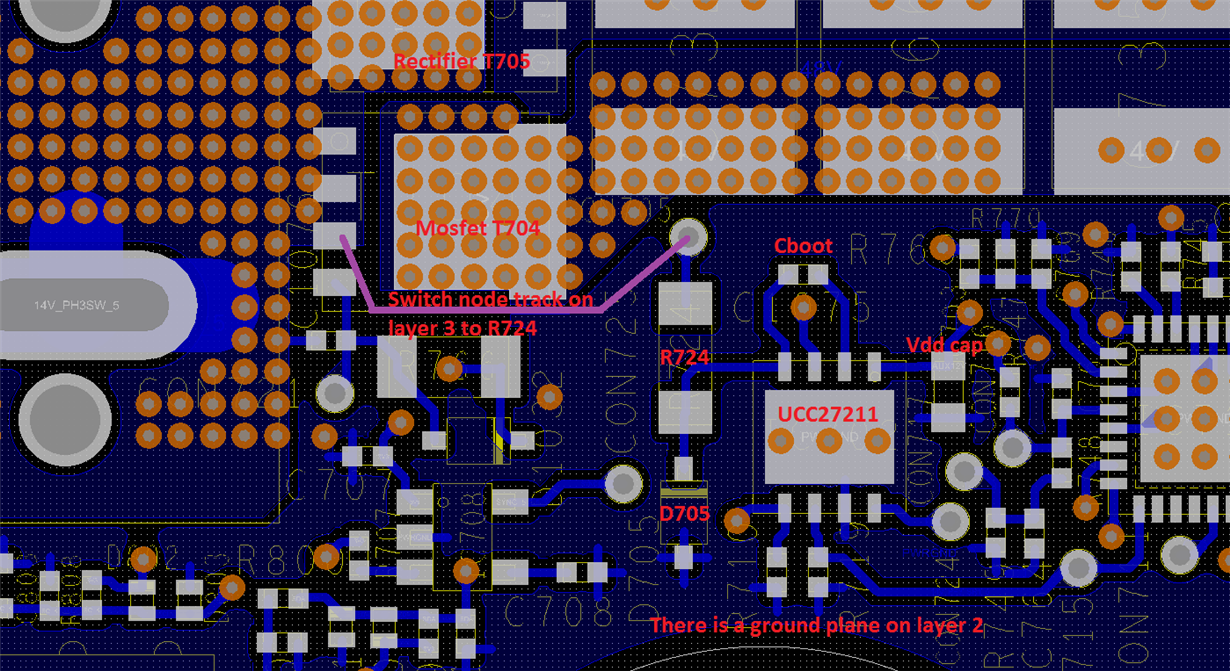

R724 and D705 is used to attempt to protect the HS pin from -ve spikes.

C1076 and C1077 reduces ringing on the gate, gave a slightly better gate waveform.

C1075 is the bootstrap capacitor.

T704 is the conduction mosfet.

T705 is the synchronous rectifier.

L702 is the output inductor, there are some electrolytic and ceramic capacitors as output capacitance not shown in this schematic.

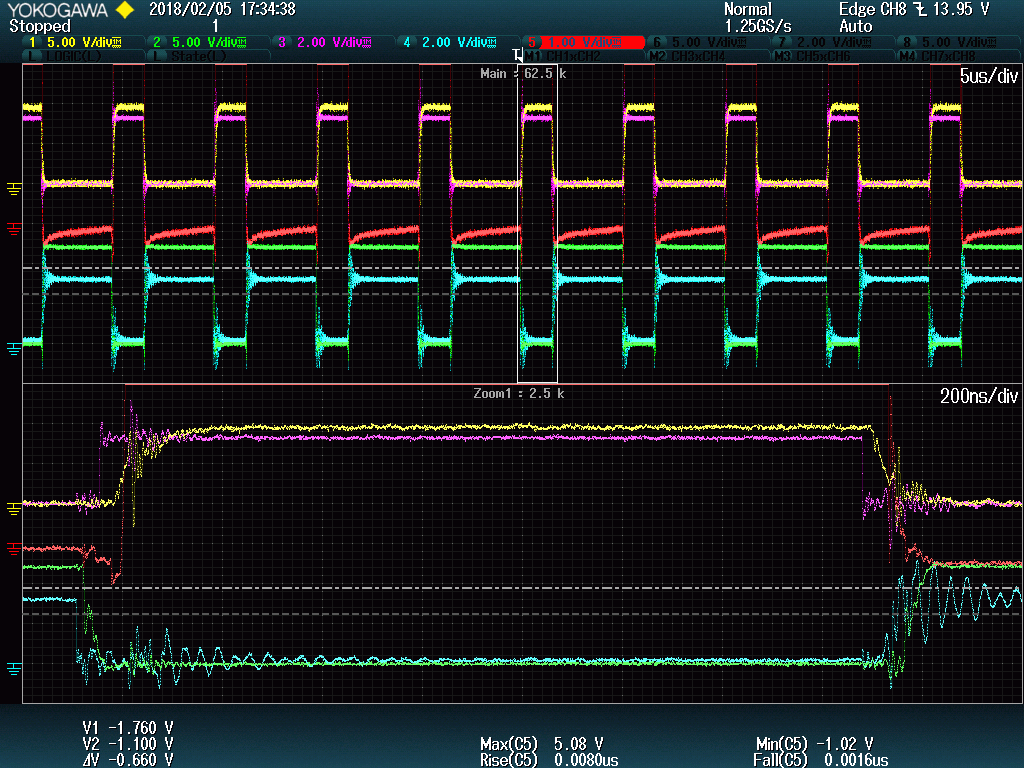

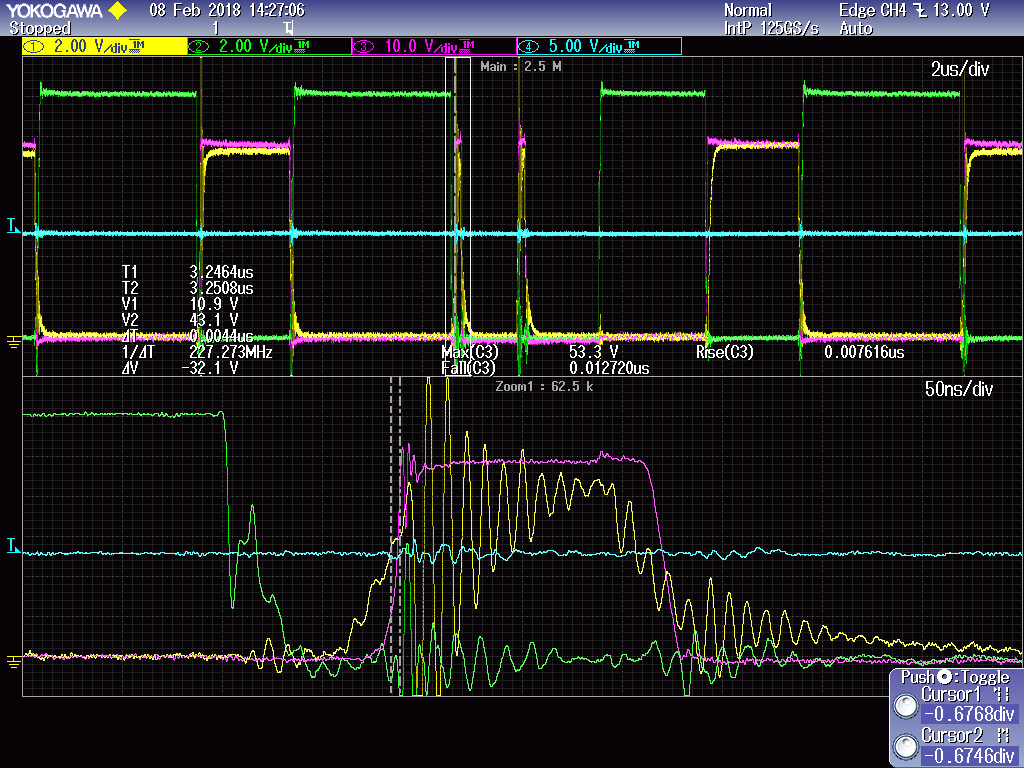

The problem is captured on the oscilloscope trace attached.

CH1=HO of UCC27211

CH2=LO of UCC27211

CH3=HI of UCC27211

CH4=LI of UCC27211

The fault happens once every 3 to 5 pulses. Basically when it receives a HI signal, it will attempt to turn on HO, but will then turn off, reattempt to turn on, then turn off again. And when its time for the Lower switch to go hi, it will have a delay before LO turns on.

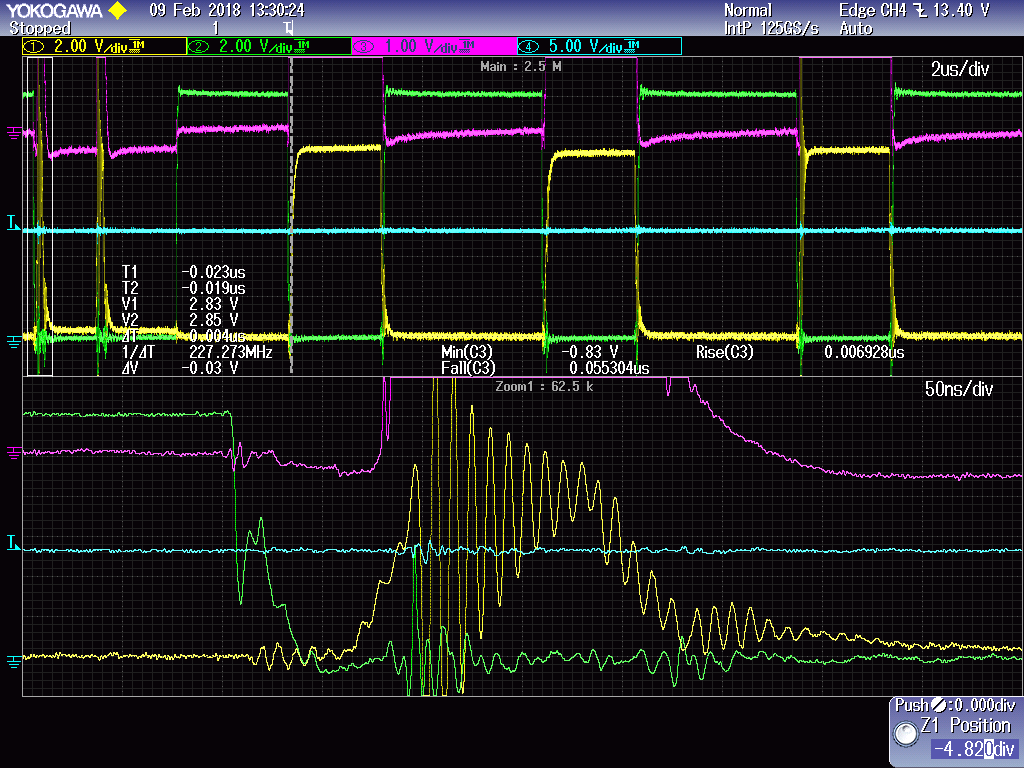

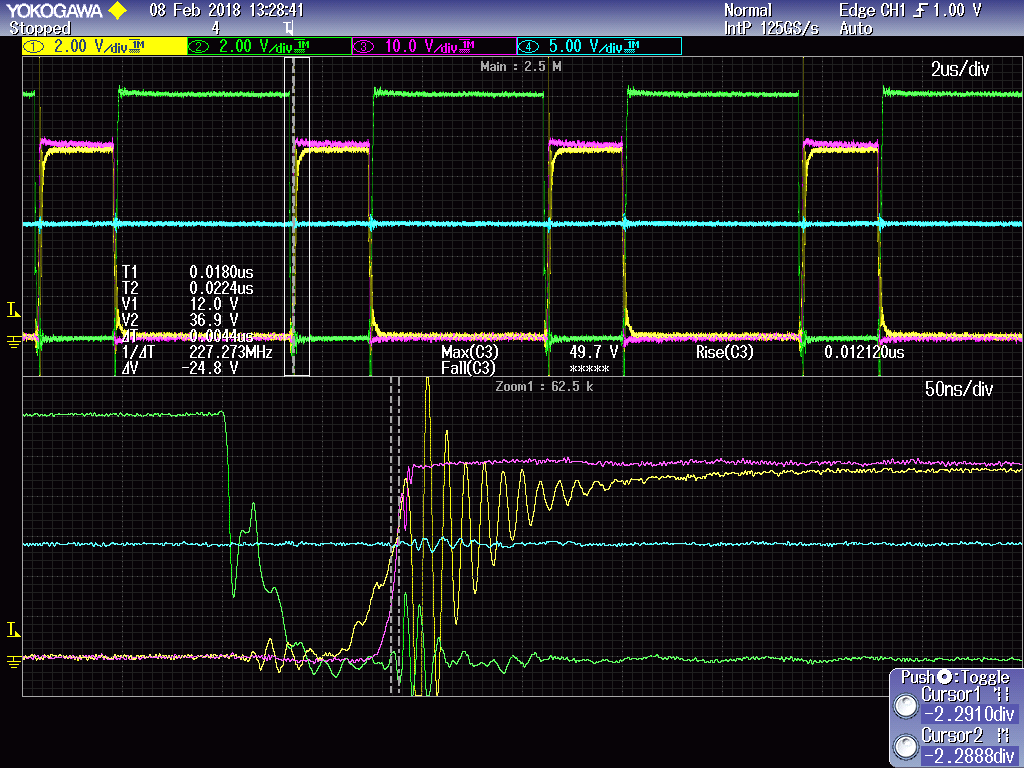

I have checked the VH pin dv/dt during the fault, and it is about 8.28V/ns (which is within 50V/ns).

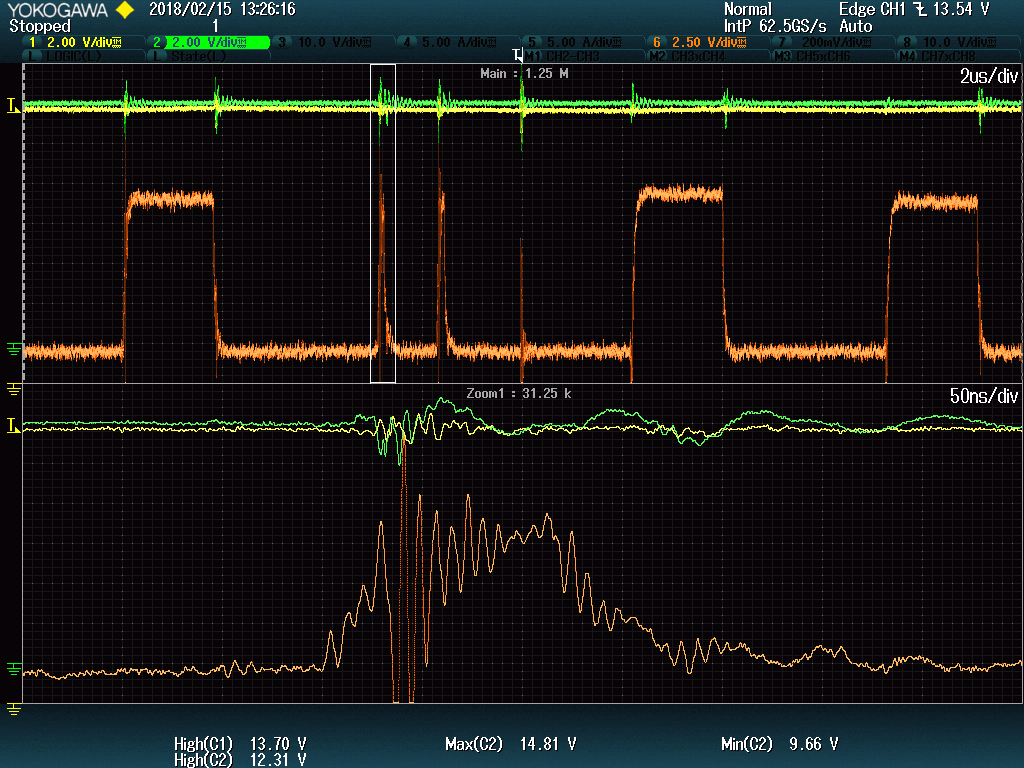

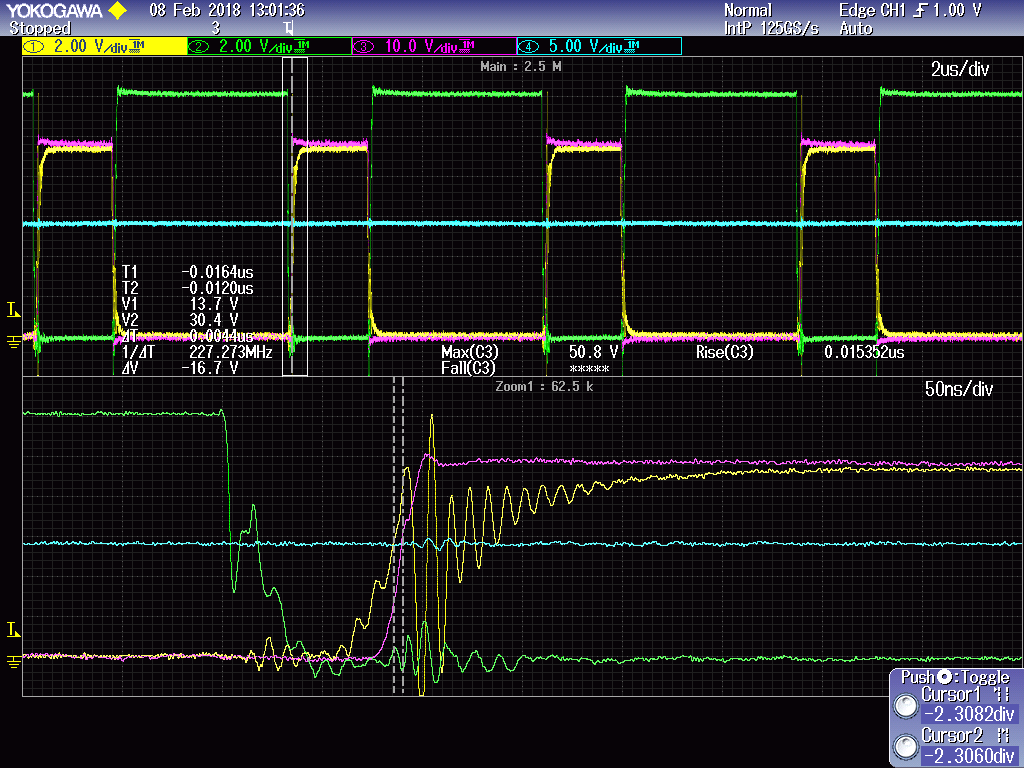

CH1=HO of UCC27211

CH2=LO of UCC27211

CH3=HI of UCC27211

CH4=LI of UCC27211

CH5=VH voltage

I have checked the VH pin Vmin during fault, and it is about -1.1Vmin (which is over -1V), however the HO pin goes down when VH is positive. CH5=VH voltage

I have then checked the VH pin Vmin when there is no fault at ambient temperature, and it is very similar. CH5=VH voltage.

I have checked the VDD pin during fault, and it is 10.2Vmin (which is above UVLO). CH5=VDD

I have a possible solution to this problem by adding an RC snubber on the switch node, this seem to helped with the problem since it is much more difficult to induce the fault with the snubbers on.

I am wondering if a product expert can give me some advice on what they think the problem is inside the gate driver.

Why it is shutting down the HO and also delays the turn on of the LO every time the fault occurs.

As far as I know, the UVLO of HS only affects the high side. I cannot see it is the UVLO of the low side from the scope measurement.

What is the time for the gate driver to recover from an UVLO fault, this can allow me to check if the timing corresponds to a UVLO trip.

The dv/dt of the VH pin is well within its rating, however I do manage to fix it by adding a snubber to slow down the switch node.

This leaves only the VH pin negative rating, but the negative spike is very similar at ambient temperature under normal condition, and I’m not sure whether it will affect both HS and LS outputs.

Any advice would be very much appreciated.

Thank you.

Kind Regards,

Raymond