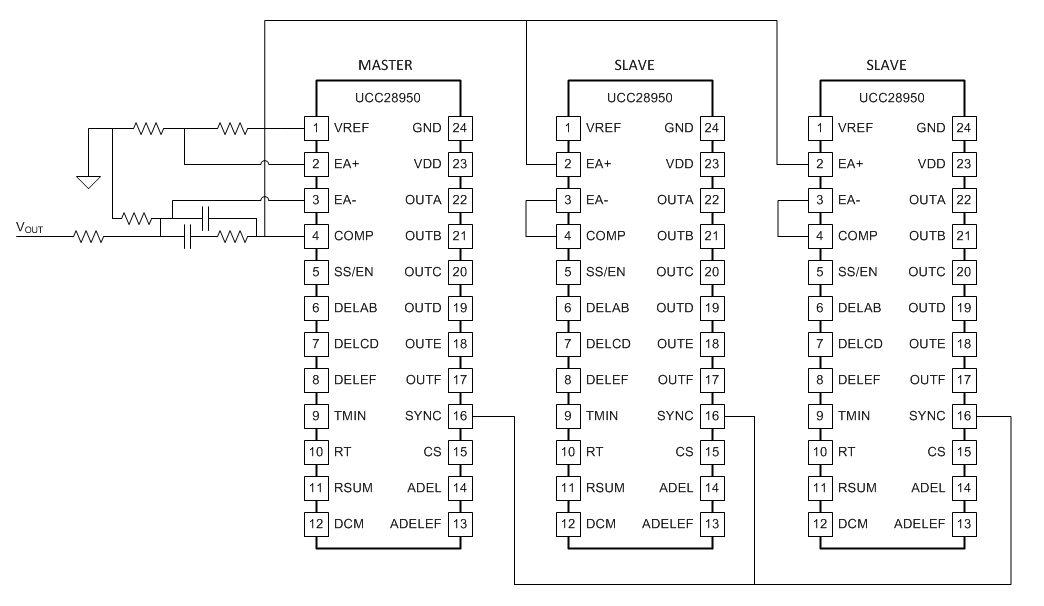

Other Parts Discussed in Thread: UCC28950

Please could somebody support with the following error I notice especially at low DC Input voltage and whilst SR is active.

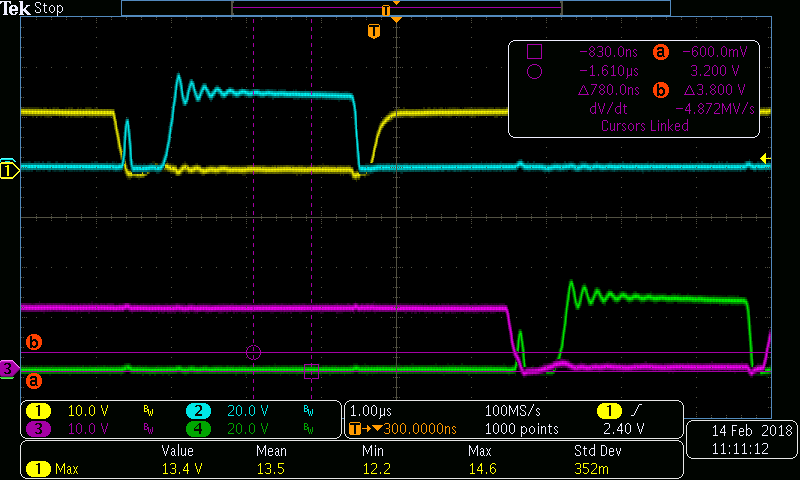

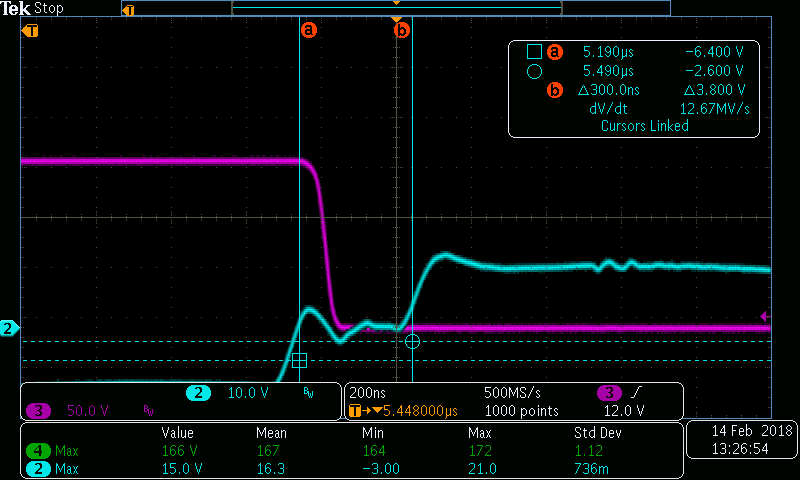

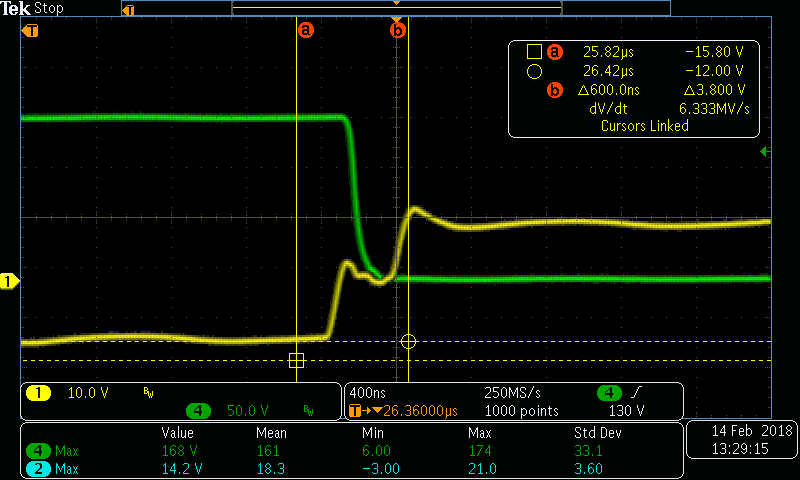

During the switch OFF period I notice a pulse in the Drain waveforms of E+F whilst monitoring gate waveform of each ( attached image ). Has this issue been encountered before?