Other Parts Discussed in Thread: TIDA-00778

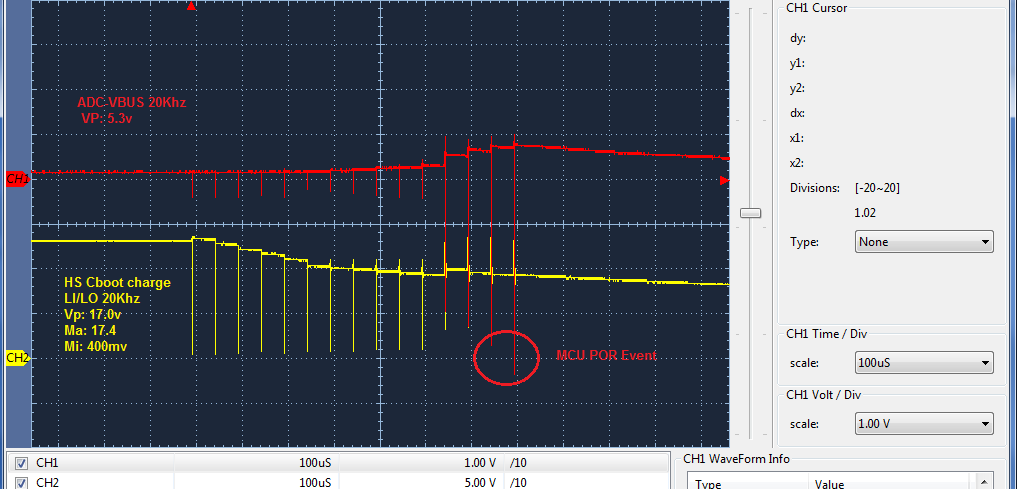

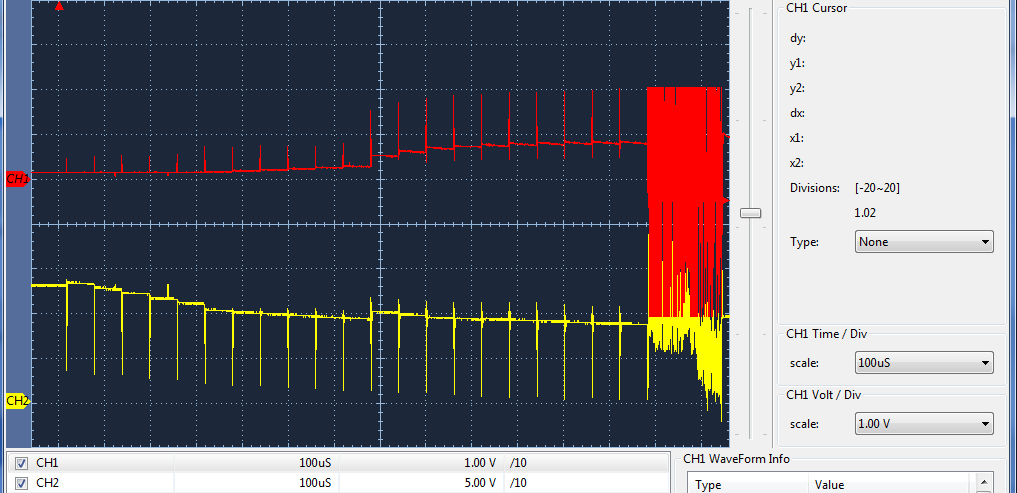

Very strange issue proven software other vendors gate drivers does not cause large voltage surge during Cboot charge cycles. This issue refers to 3 phase commutation and 24VDC bus supply rising to over 90vdc with inverter loaded or not. A custom PFC was resolving 80v-90v PWM surges controlling DC bus voltage. That was the only way Cboot cycles could ever succeed let alone FOC commutation drive a connected motor to 7600RPM.

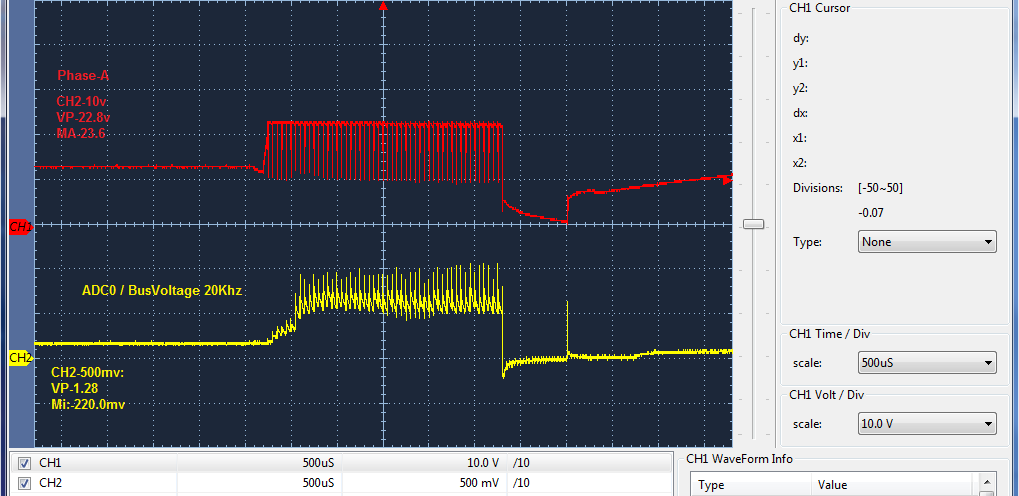

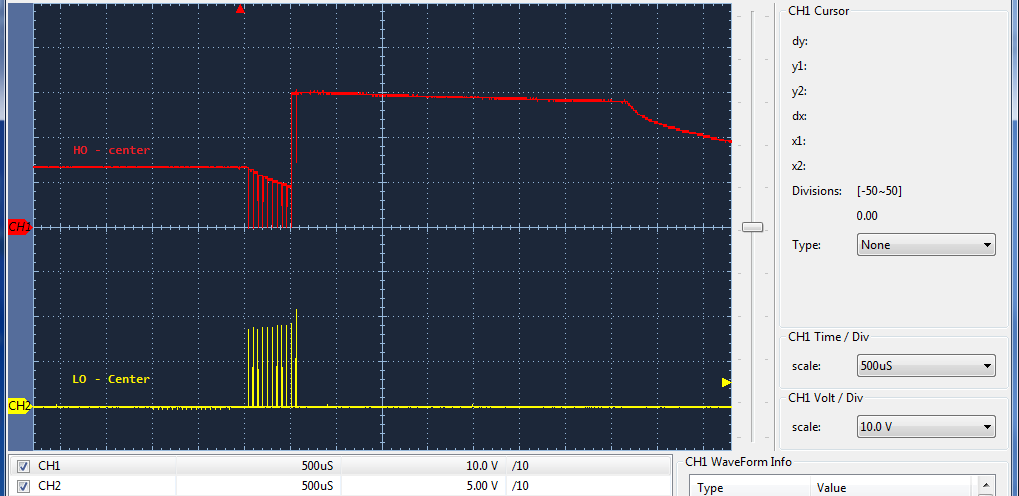

The PWM frequency 20Khz driving 500ns Cboot duty cycle (1%), user settable charge time 1-255ms. Capture below taken single phase (1/2 bridge), all phases resemble similar pattern though signals cut off in 2ms when PWM fault handling has been enabled. Otherwise the 500ns Cboot pulses POR the MCU very abruptly. UCC pin 4 (EN) was kept high 3v2 (enabled) at all times of this testing.

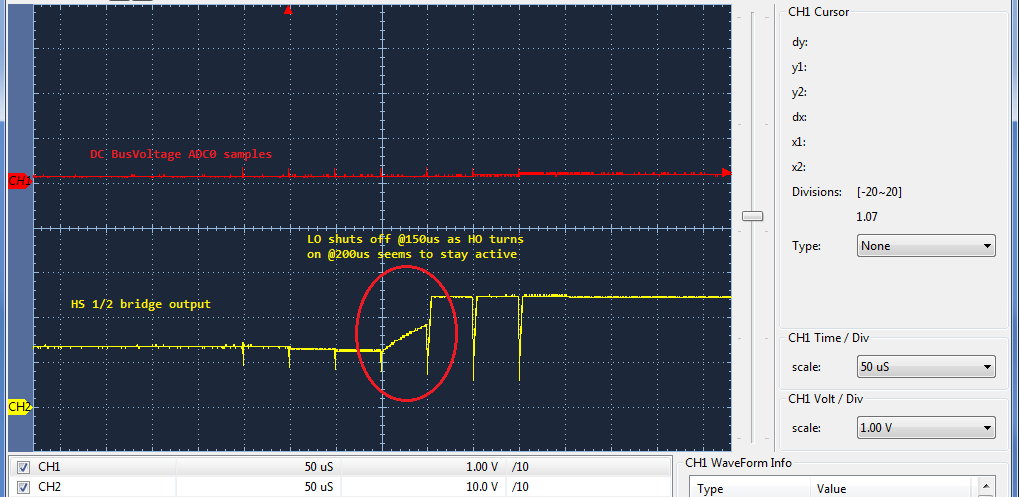

How could HO drives stay on during Cboot cycles when the MCU PWM control block keeps all 3 HI (low) during Cboot cycles? Do we not expect H0 side should always be low during Cboot cycles or have I missed something in how 1/2 bridge shoot through occurs? Perhaps these 3 gate drivers are messed up in some way and do not follow proper 1/2 bridge switching conventions. The LO side gate drives pulse rising edge from ground producing the odd wave form below. The LO side seems correct in my opinion but not HO staying active during Cboot cycles so the HO single is some how being inverted.

CH2: ADC0 channel input reporting DC voltage. Signal represents 70-80V peaks from 24VDC supply low/left side of signal prior to undesired POR of MCU, far right.