Other Parts Discussed in Thread: TIDA-00778, ALLIGATOR

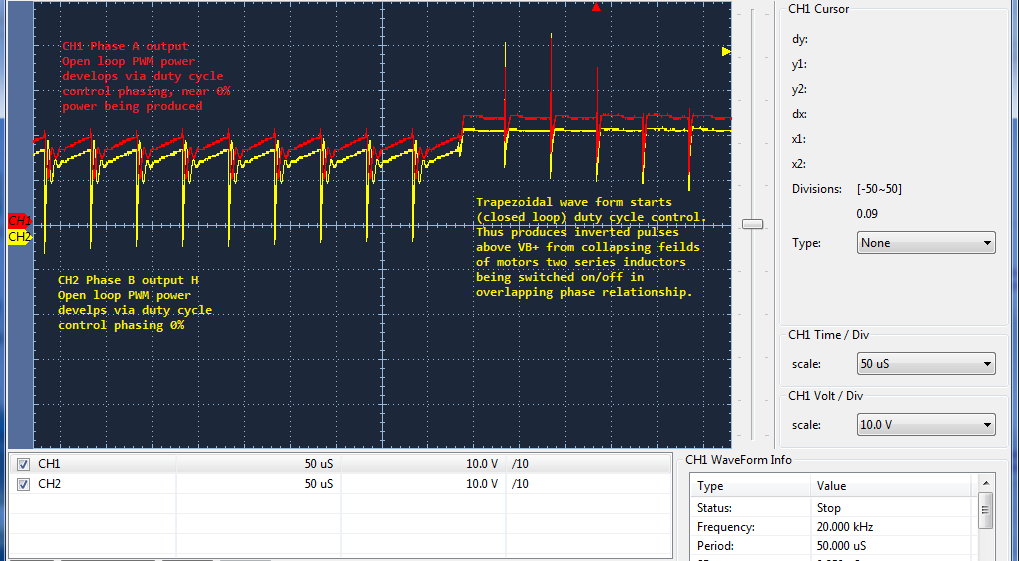

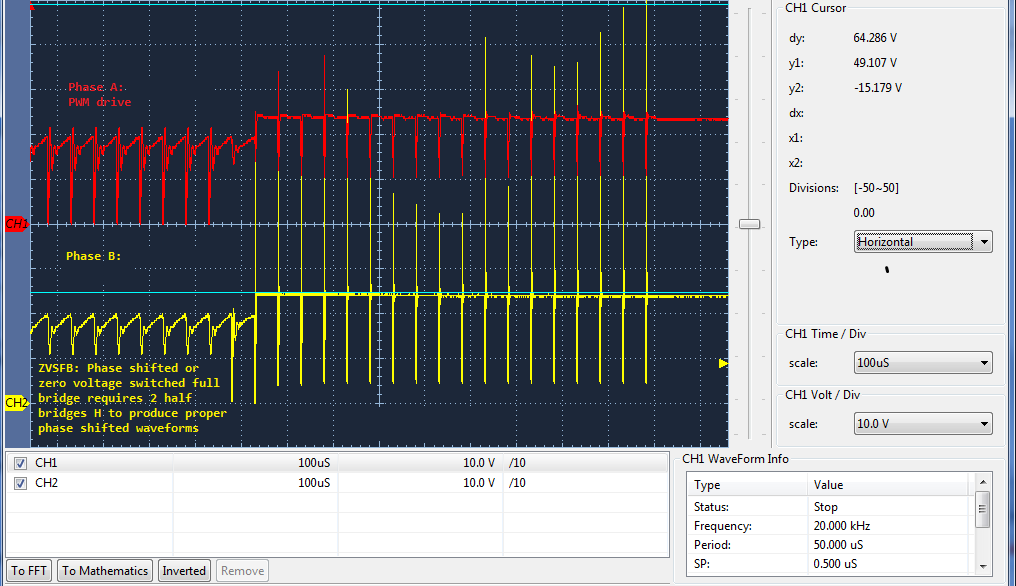

It seems we are unable to consistently produce a proper looking pulse width under or above 1us from MCU driven PWM generators as HI/LI are individually being delayed 40ns by UCC.

Previous system gate drivers only inserted delay matching on LO input and produced 8-80Khz PWM near 100% duty cycle on LI/HI via LO/HO. That is a joint effort requiring two UCC gate drivers and two synchronized PWM generators in Co-partner field phasing rolling into a third UCC for three phase commutation schemas. A-B, A-C, B-A, B-C, B-A, C-A co-partner hard switched half bridge schema requires 6 codes to drive inverter.

Can the UCC by delaying separately LI & HI inputs 40ns maintain compatibility with TM4C1294XL PWM peripheral generators in co-partner phasing? From this point it seems the 40ns delay matching is obstructing proper pulse generation of co-partner gate drivers. When both HO/LO of co-partner gate drivers is required to develop such pulses, 1/2 the pulse generation is often MIA or being inverted upside down above supply rail, not always but more often than expected.

It appears the DC inverter in not keeping synchronous to the PWM generators at all times and produce very distorted pulses and widths in the process. Even the HO copartner that does not produce an inverted pulse at the end of each period is distorted and does not reach down to mid supply.