Other Parts Discussed in Thread: TIDA-00778, , TIDA-00909

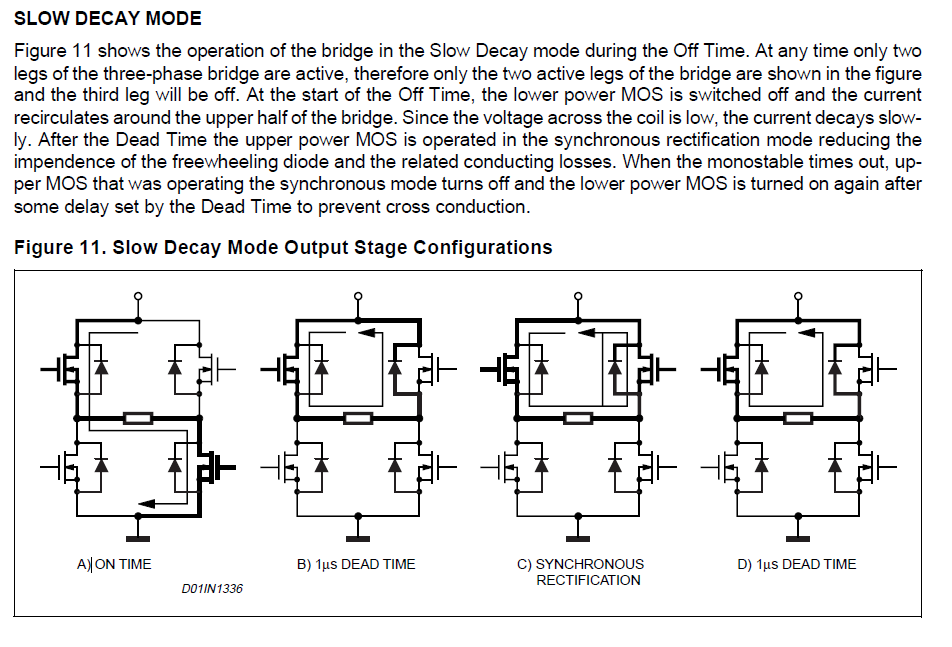

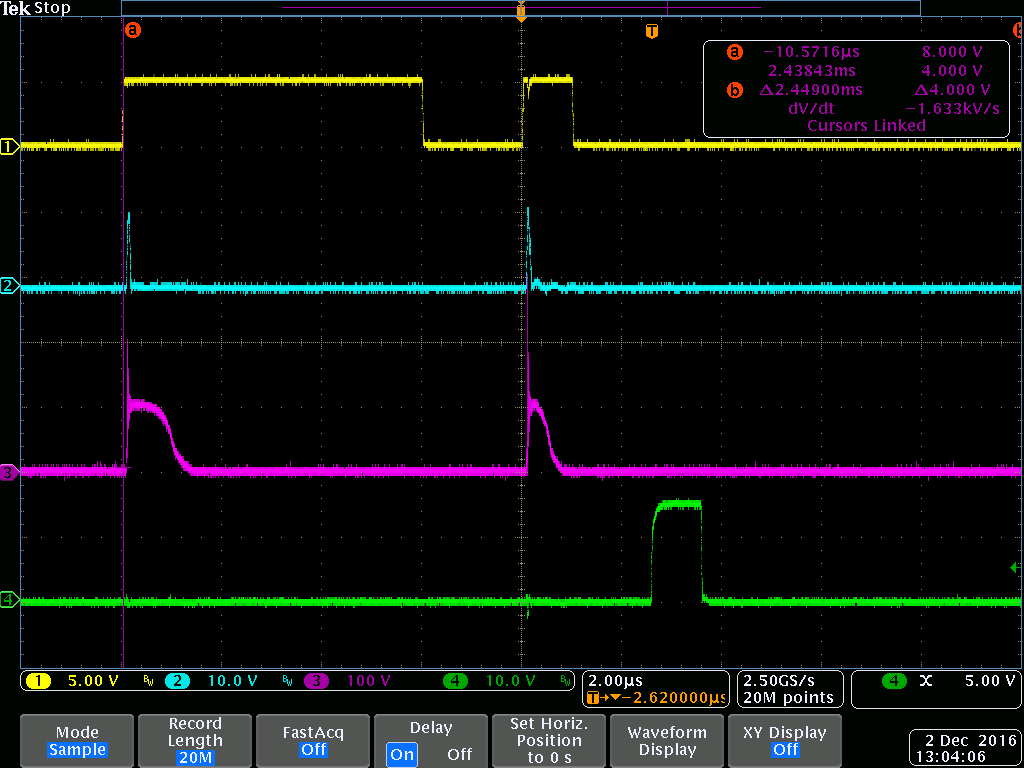

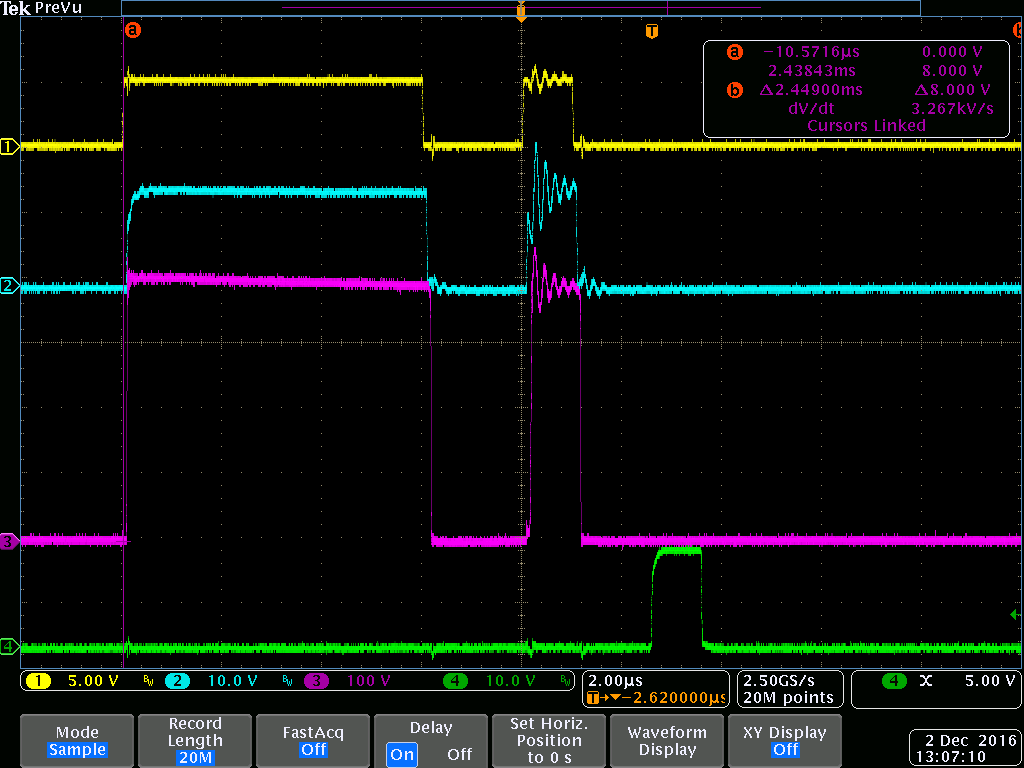

We capture certain position of LO ring ghost or follow HO ring and or undershoot may be HI/LI driven cause? We notice 140ns 1/2 bridge dead band delay make HO incorrectly produce 140ns positive pulse when it should be delay time only. If we make 100ns delay the HO pulses diminish into a minimal sine wave when HO transitions from high to low but not entirely in every case. The Gton=530ma and GtOff=1.5amp yet we have never heard of Toff switch node ringing or odd HO/LO ghosting captures show below. Especially when inverted LO is producing short HO pulses between the main trapezoidal waveforms. Only HI is inverted and derived from LI during delay periods but only for a previous high to low transition of HO in any current output period does a delay occur.

Perhaps UCC shorter Tfall 30ns, 125ns propagation delay and faster NFET Toff 24ns delay, 8ns fall time allow even shorter dead band period than 100ns? How minimal can 1/2 bridge dead time delay be made when NFET Trr is 144ns Nom to 288ns Max? Can some HI/LI dead band generator phasing be causing random pulses in the HO period but only when LO high to low?

Updated capture below after bravely setting dead band generator 60-80ns. Most documents suggest dead band delay be set 1.5 - 2 times the minimum pulse width. So 0.8us (800ns) minimum pulse width makes dead band delay 1.2us but not 80ns. Perhaps the PWM generators minimum pulse width is set to high in software algorithm!