Hi All,

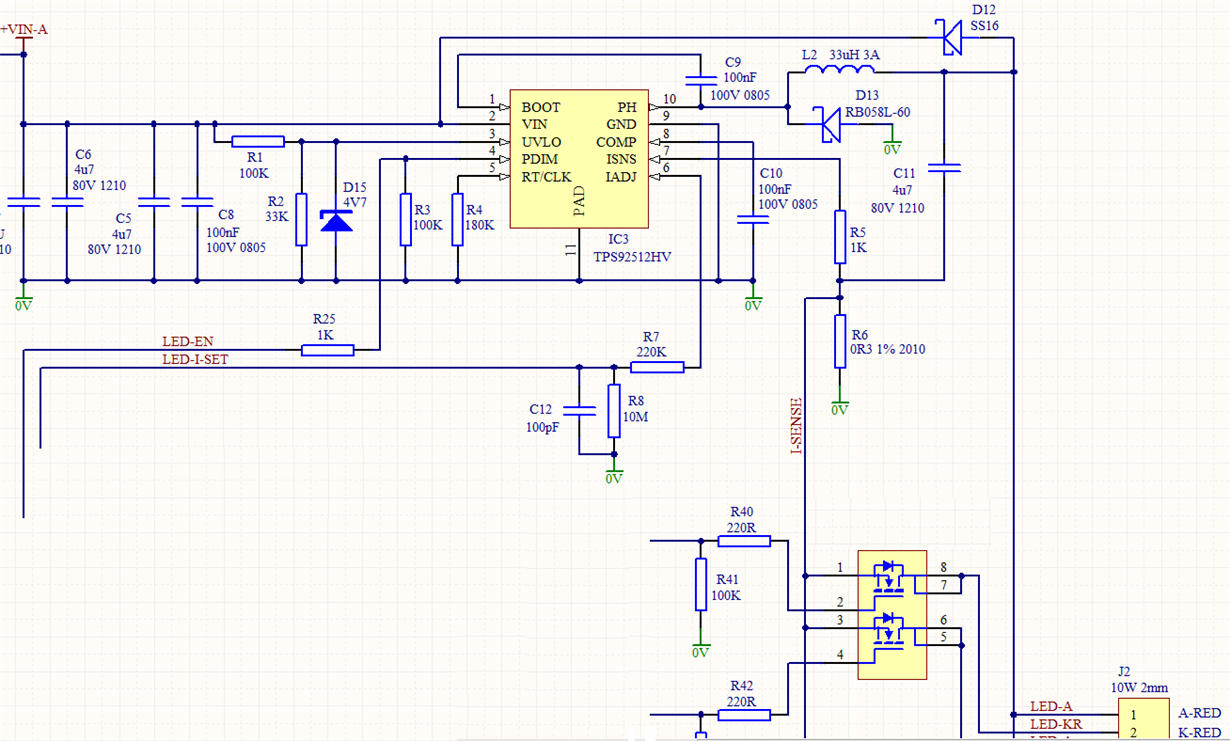

I'm considering to use a TPS92512 chip to switch it's output to one of three LED branches of different colours (R,G,B) and run a current of 850mA~1A through it.

Schematic is attached. Vo is connected to three branches of LEDs with 3 high power LEDs in each branch in series (7.5 to 11V forward voltage depending on colour) but each branch has a Mosfet switch to ensure only one branch is ON at any time. Current level can be controlled through Analog Iadj pin.

Two concerns I have is:

1. If Vin falls close to total forward voltage of LEDs, driver goes out of regulation. What behavior it will have in terms of how much current it will push through LEDs in that mode? Would Iadj pin be in charge of controlling output current when chip is not regulating? How about PDIM input?

VIN shuold be high enough to drive LEDs but if for some reason (drooping, running below rec spec) it was not, I would like a dimmed and safe operation to ensure LEDs or chip itself not damaged.

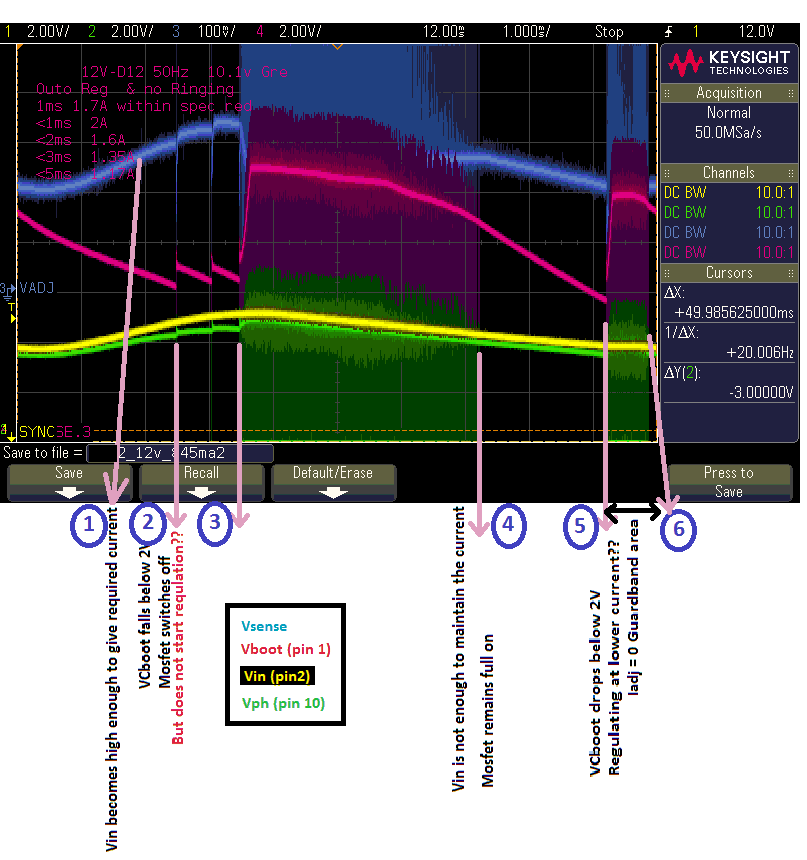

2. When Vin falls below certain level, I see periodic negative spikes on PH pin until VIN rises to above a certain level and regulation resumes. Apparently Cboot falls below 2 V:

(Red: Boot, Yellow Vin, Green Vo,Blue Vsense)

Could these pulses be resulting in EMC issues?

3. Accidentally noticed if RT/CLK pin is touched by finger (discharged by touching Ground beforehand) chip blows up in less than a second!!!

Well although this cant happen in normal operation but wondering why is this happening. I can consistently blow up as many chips as I want by this.

I would appreciate any comments.

Thanks

Matt