Hello,

Has anyone had any experience using resistor test loads on the TPS61180? Using resistors, we found the Fault protection PFET will not properly turn on. With the Fault PFET bypassed, resistor test loads perform fine. We've found a possible workaround to allow the Fault PFET to turn on, and would like to understand if our solution will be reliable in production test environment.

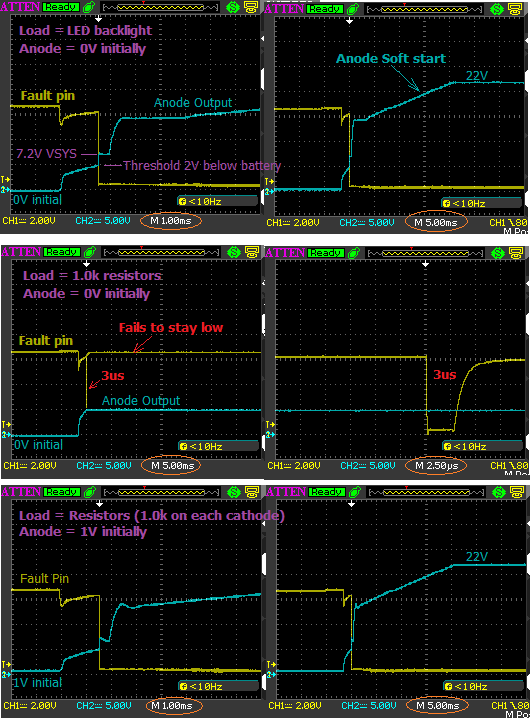

The LED loads in our product application have seen no issues with the Fault PFET turning on, which uses 7 series LEDs in each string, resulting in a Vout (Anode) level of about 22V. ISET = 57k for 21.6mA. System Vbat = 7.4V nominal.

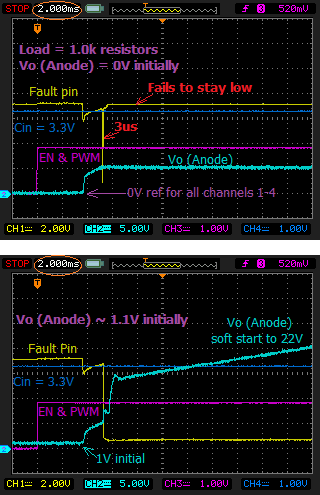

For the 1.33k resistor loads in our test fixtures, with the Fault PFET bypassed, Vout properly rises to 29V. But with the PFET in line, it fails to turn on using various resistor loads (such as 1.0k resulting in 22V), and various IFB combinations by disconnecting/disabling outputs with 10k resistors to ground. Varying the sequencing of the EN and DCTRL (PWM) pins also does not help. Bypassing the PFET always allows the various resistor and IFB combinations to perform as expected.

Our workaround solution, we discovered, is to first enable the TPS61180 for several milliseconds, long enough to allow the internal soft start resistor to charge the Vout cap to about 5V (Vbat - 2V). Then release the enable for several milliseconds and then re-enable. The Fault PFET then properly starts every time on the second enable. If we wait too long (several seconds) before disabling & re-enabling the second time, the Vout cap will discharge below 1.0V, and the Fault PFET will again not start. Vout must be above 1V to allow the second re-enable to work.

The 1st row of waveforms below show Vout (Anode) and the Fault signal with LED loads. The 2nd row of waveforms use resistor loads with Vout initially at 0V resulting in the Fault output only remaining active for 3us. The 3rd row has Vout initially at 1V resulting in similar waveforms as the LED load.

We are fine using this workaround procedure for our production tests, as we can re-enable well before the output cap discharges much at all, remaining well above 1V. But without understanding the fault circuit operation and thresholds, we have concern if this workaround is reliable. Could we have false test failures over many thousands of boards? The datasheet does not provide enough circuit detail to understand the fault thresholds and timing.

We prefer resistor loads over LEDs in our production test environment for better measurement stability and correlation across several test fixtures.

Thank you very much.

Norbert