I am currently evaluating TPS92641 LED drivers on prototype boards. The application scenario is as follows:

- Input voltage: 12-28V

- Output voltage: 2-5V (single LED)

- Output current: 500mA - 5A

- Switching frequency: currently 300kHz (will maybe lowered to 250kHz to ensure minimum on time in worst case operating conditions)

- Dimming: Analog + UDIM (1.5kHz)

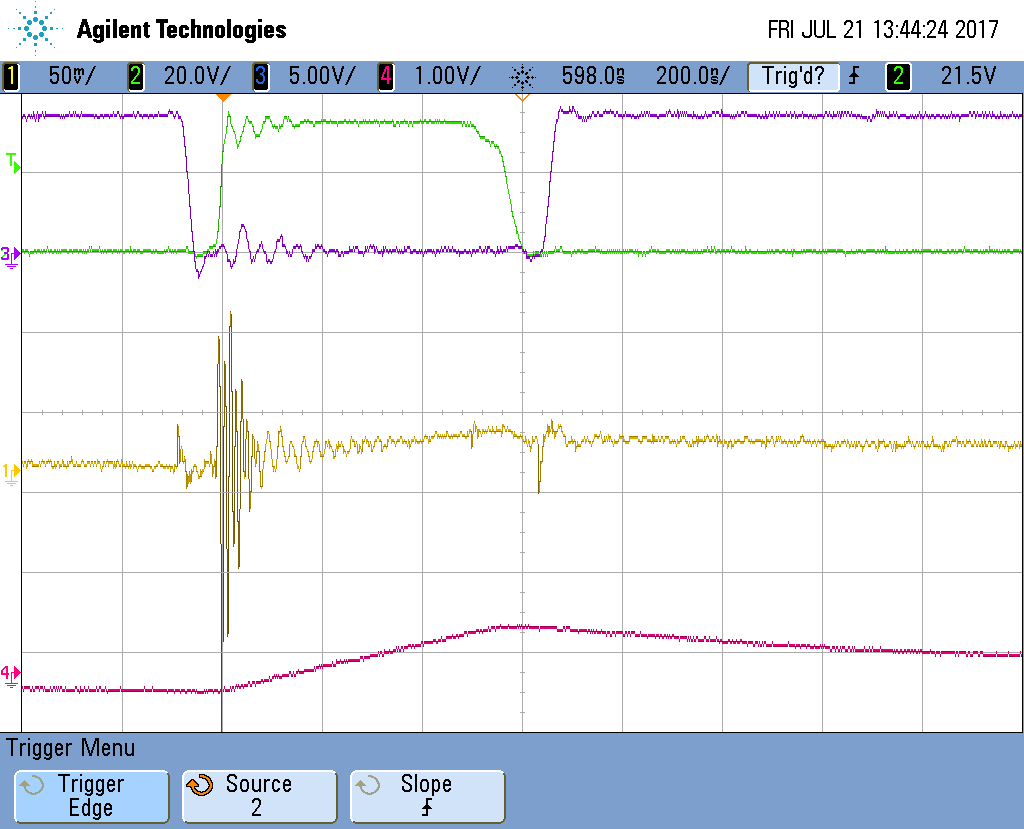

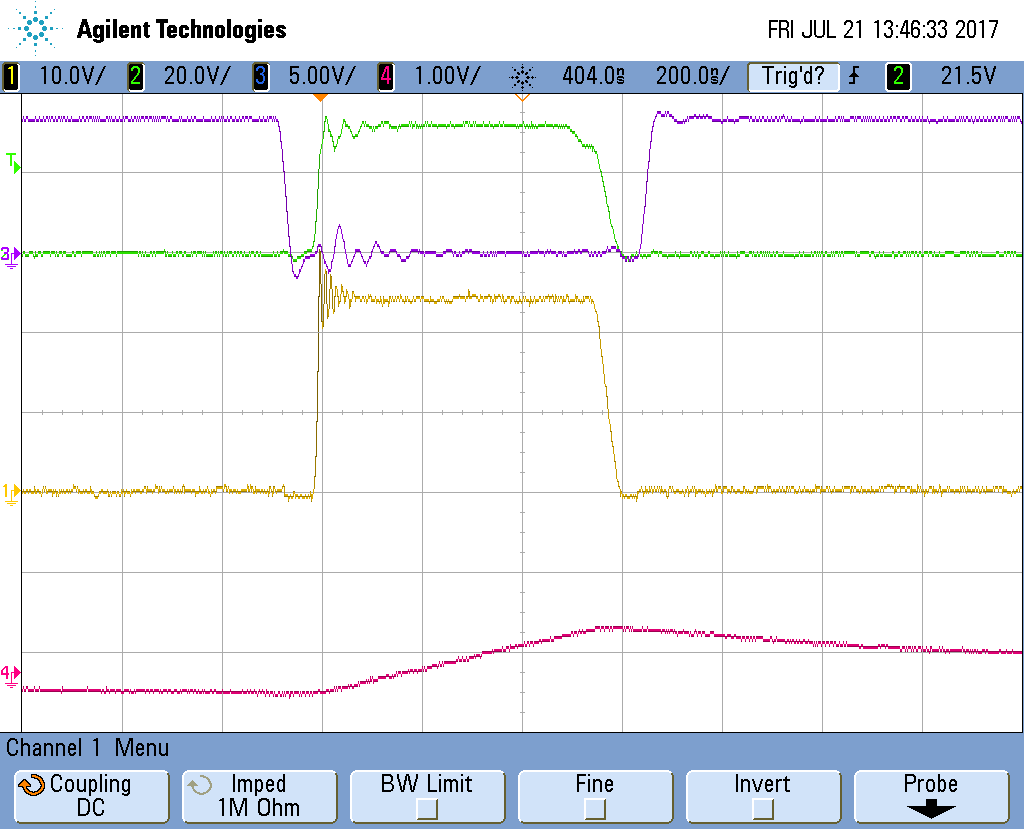

The driver is functional, but both switching frequency and duty cycle are not stable. When the Rf series resistance is set to 470Ohm, I see double switching pulses (it looks like the overcurrent behaviour but with shorter gap in between the pulses). By increasing the resistance to 10KOhm this behaviour can eliminated.

My sense resistor is set to 20mOhm to keep power dissipation in an acceptable range for the higher output currents, which the circuit should be able to drive. Is it necessary to increase Rf when using such low resistance values for current sensing ?

Regarding the compensation capacitor: Which value would be applicable for my design ? Is 100nF the right choice for the PWM dimming application by using UDIM ?

Another question is related to the dimensioning of the on-time circuit. Is there any lower limit for the Con capacitance value ? I want to keep the power dissipation of the Ron resistor as low as possible and therefore it is necessary to use a capacitance <1nF, which is used in all reference designs I found so far.

The entire circuit is depicted in the follow schematic, T15 and C36 are not populated. I would be grateful for comments and hints regarding the dimensioning.