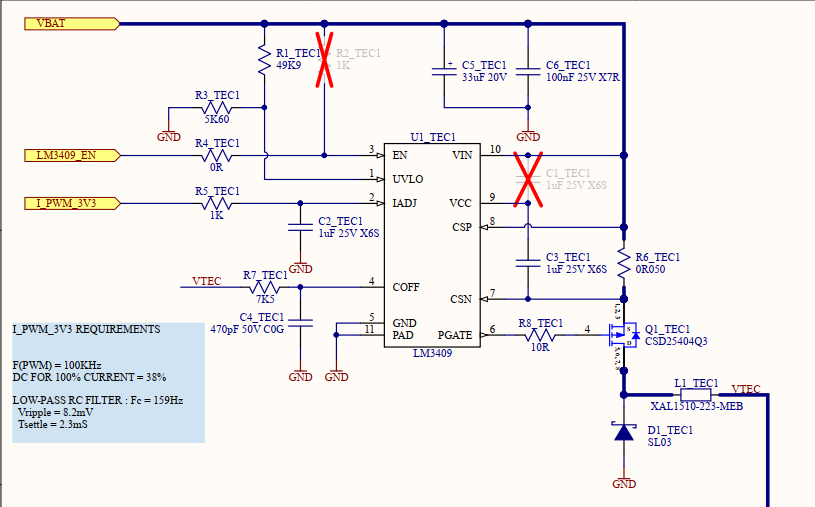

I am using the LM3409 to drive a current controlled device (NOT an LED) with the max output current set to about 4.85A with a 50mOhm sense resistor. However, I intend to use the IADJ pin to reduce the current dynamically to control the output device. But for now, I'm just testing the circuit to make sure it is working as expected--and it is not.

The issue is that when the output device is connected (either with the on-board H-Bridge OR done manually) the output current immediately jumps to the limit of the lab bench supply with programmable current limit. For now I'm just using a 0.1ohm 10W power resistor to make things easier.

I have scoped out (attached: dark blue is IADJ, light blue is EN) the IADJ pin and EN pin. I dynamically control both as this is required for the intended device. You can see that every 1.2 seconds or so I am turning the LM3409 off and the IADJ pin is driving to 0V. Then, the output h-bridge is switched, the LM3409 is enabled again, then the IADJ pin is ramped up to its maximum (~350mV in this case). This is all done to reduce thermal stress in the output circuit, though the final application will have much longer periods by about 100x. I've shortened the time to make testing easier and quicker. This scope was taken when the output device was removed, so no load. That also proves out that I'm not getting dead-short of h-bridge FET's.

My understanding is that with IADJ = 350mV the output current should be limited to 0.35/1.24 of the max current set by the sense resistor. So in this case that would be ~1.4A. But when I connect the load, I see the power supply hit the current limit with output current up to 5A! So for some reason the current limit isn't being observed by the LM3409.

I populated C3 because, initially Q1 had a much larger gate capacitance as per the discussion of page 22 of the datasheet. I haven't updated the schematic to account for that yet, though my understanding is that this would just cause a bit more inductor ripple which is little concern right now.

Any idea on what is going on or how to debug what is going on?