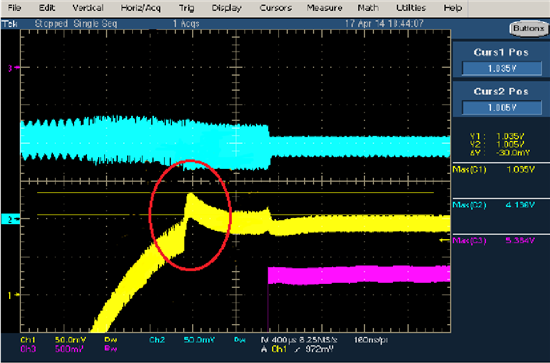

it seems internally generated and synchronized with PGD pin.

Is there any workaround to prevent this voltage ripple?

My customer wouldn't like to change soft start time, so please advise me in other ways if possible.

--------------------------------------

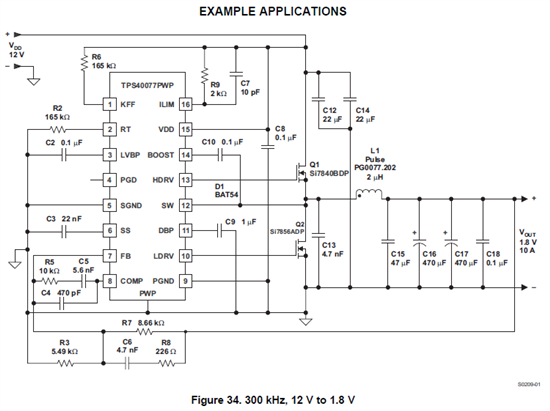

The test condition is following.

VDD=14V

VOUT=1.0V

IOUT=10A

--------------------------------------