Hi

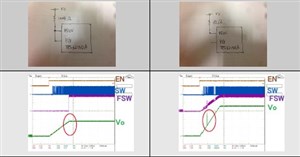

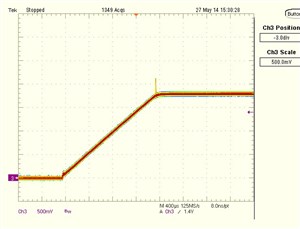

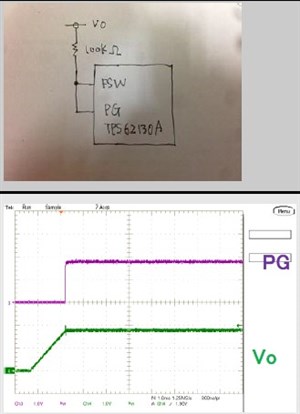

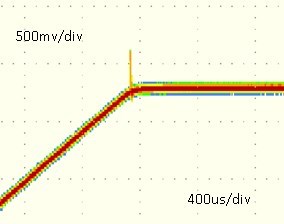

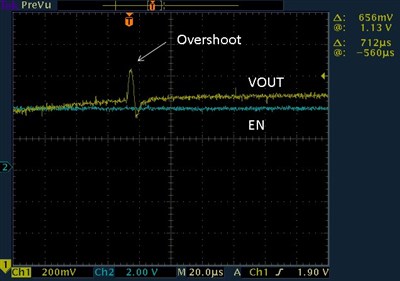

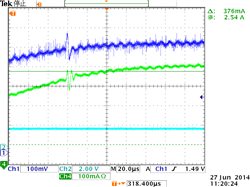

The overshoot has been confirmed to the output when a customer evaluated in the circuit, such as the following.

It does not occur when it is used in fsw=2.5MHz mode , however it occur when the frequency is set 1.25MHz.

We guess the overshoot has occurred when the frequency is changed at powerup.

Is it normal behavior. Are there any solution for this phenomenon if it is not.

(condition)

Vi=10V, Vo=1.8V,Io=1.6A, fsw=1.25MHz

(additional information)

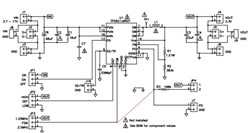

These phenomena are seen in the board of the customer, I have also seen your EVM which is connected with a lead wire FSW terminal and terminal PG further.

Best Regards,

Koji Hamamoto