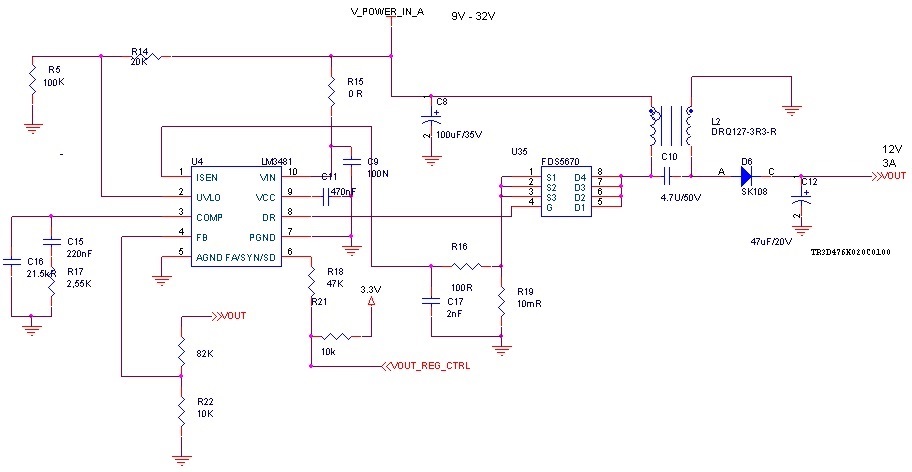

I am developing a dc/dc sepic converter using the lm3481.

these are the parameters:

Vin: 9V - 32V;

Vout: 12V

Iout (max) = 3A

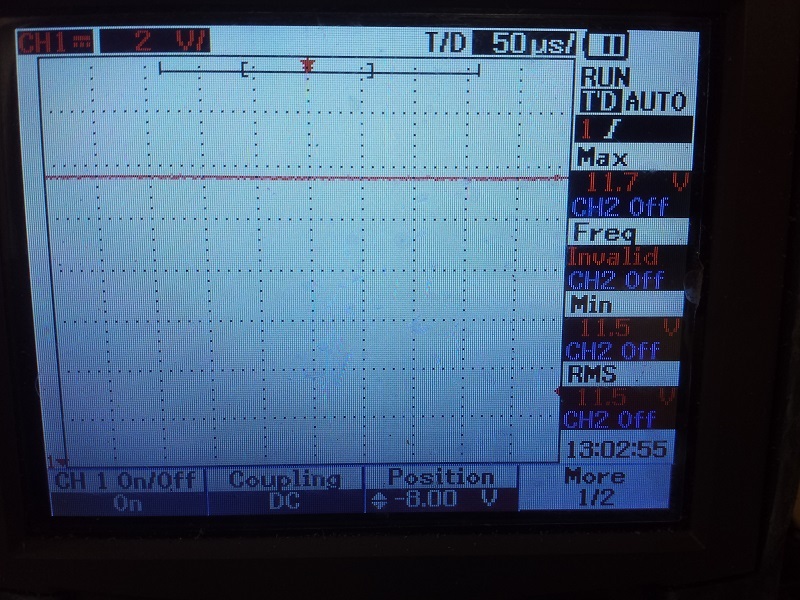

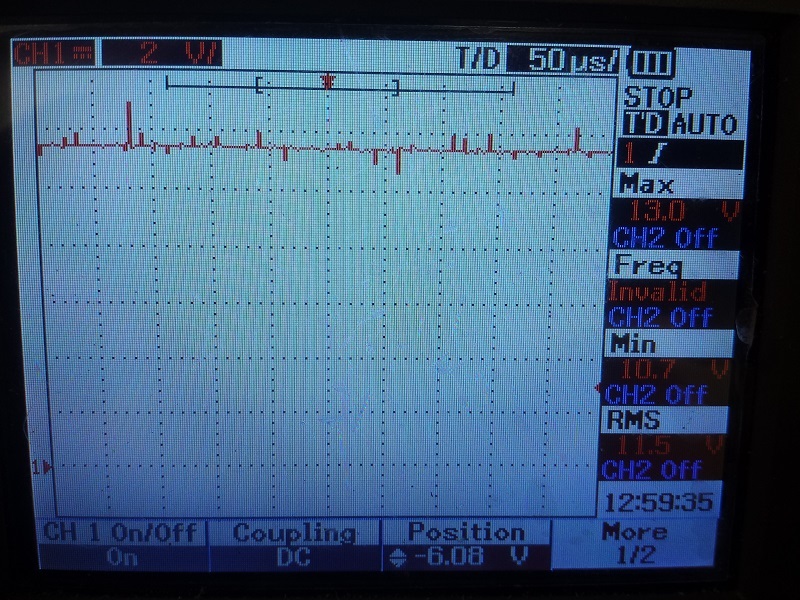

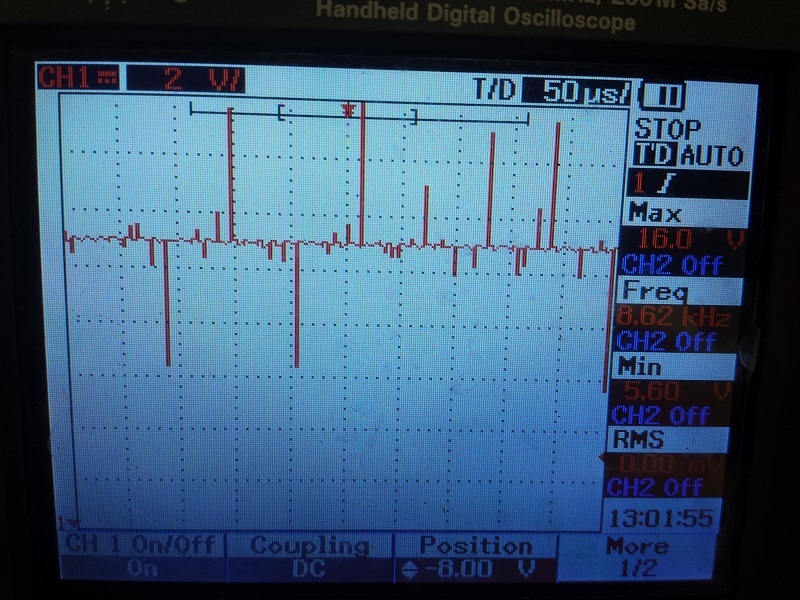

When my device is On with no load the regulation looks OK. But when I increase the load it starts to show some spikes on Vout.

It seems to be the same problem of another post (LM3481 Sepic Circuit, Spikes on Vout), still not solved.

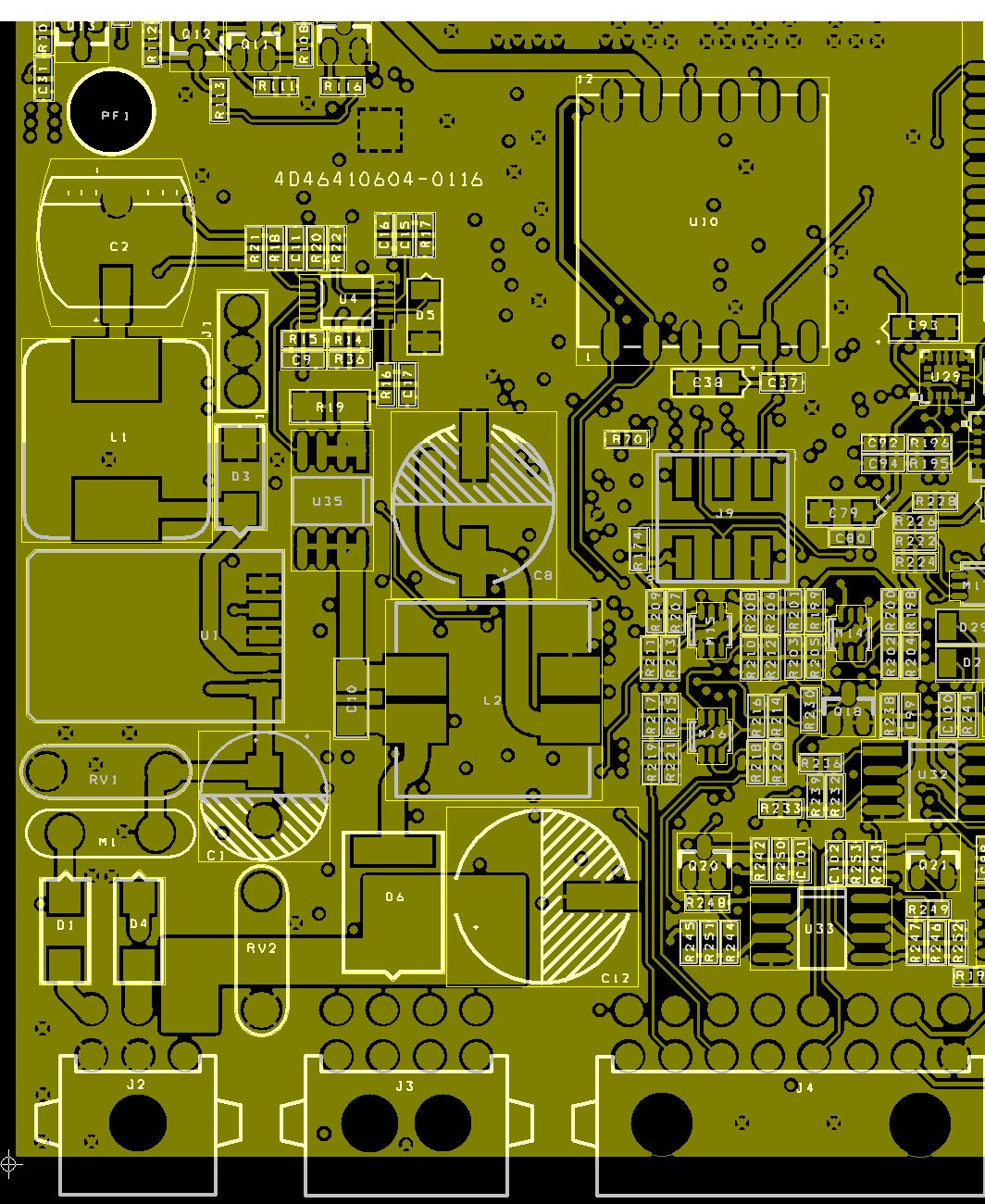

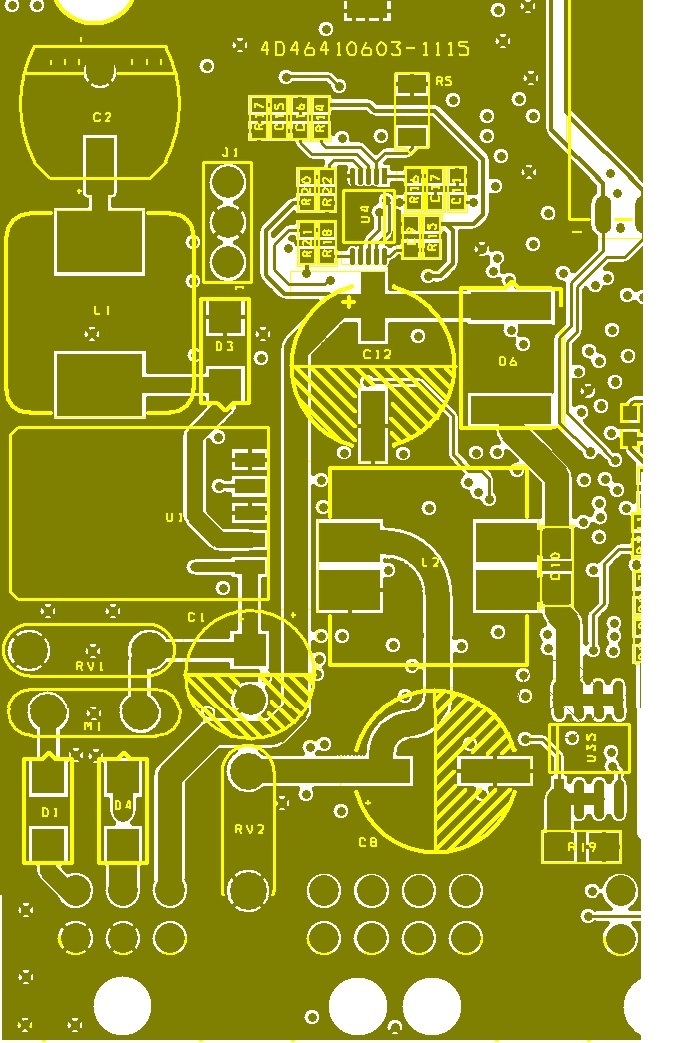

I suspect of layout, but I'd appreciate if you could have a look at my schematic and layout to confirm that.

Here are the pictures of schematics, layout and scope (no load, 400mA and 1,5A)

Thank you

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.