Other Parts Discussed in Thread: CSD88539ND

Dear E's,

During evaluating several different FETs for reducing switching losses, TPS40170 starts to run in hic up mode, when ever a fast FET pair is used.

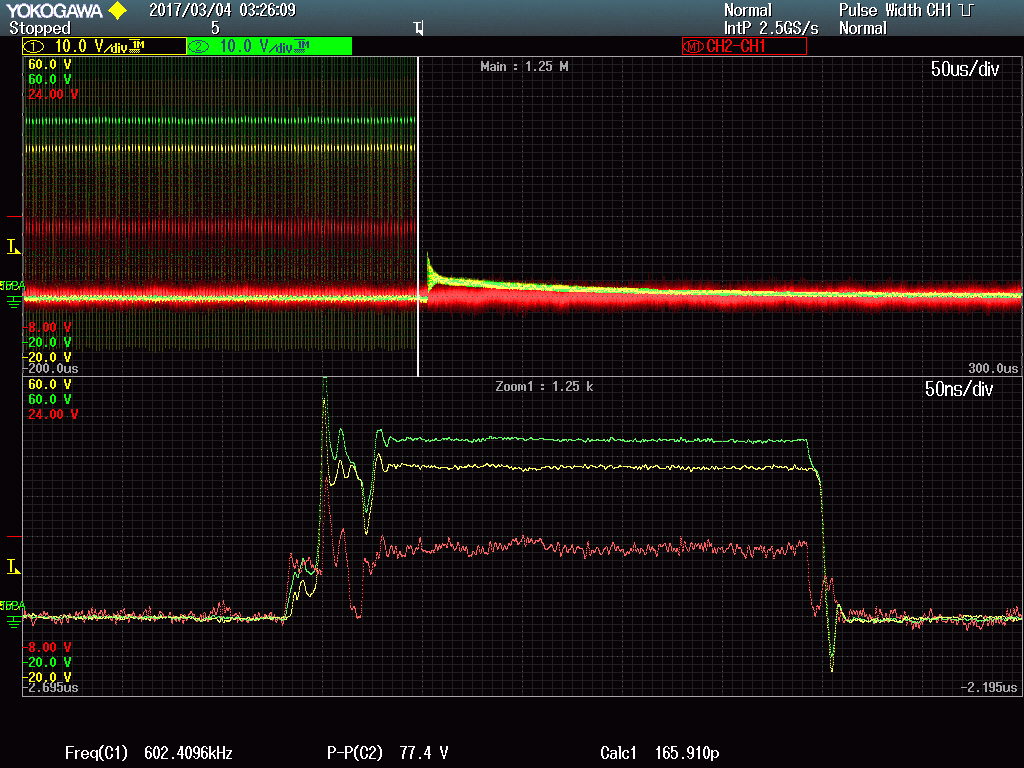

Looking at slow start voltage across C611, it looks like a over current is triggered each time, because this voltage always ramps up and down like a saw tooth.

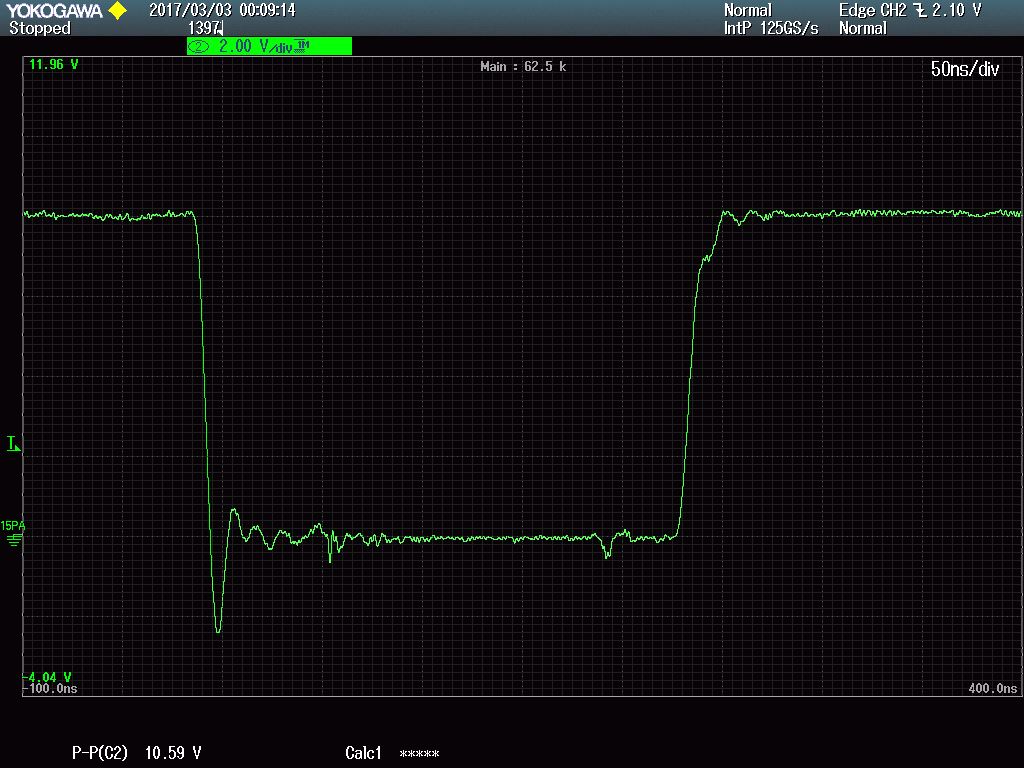

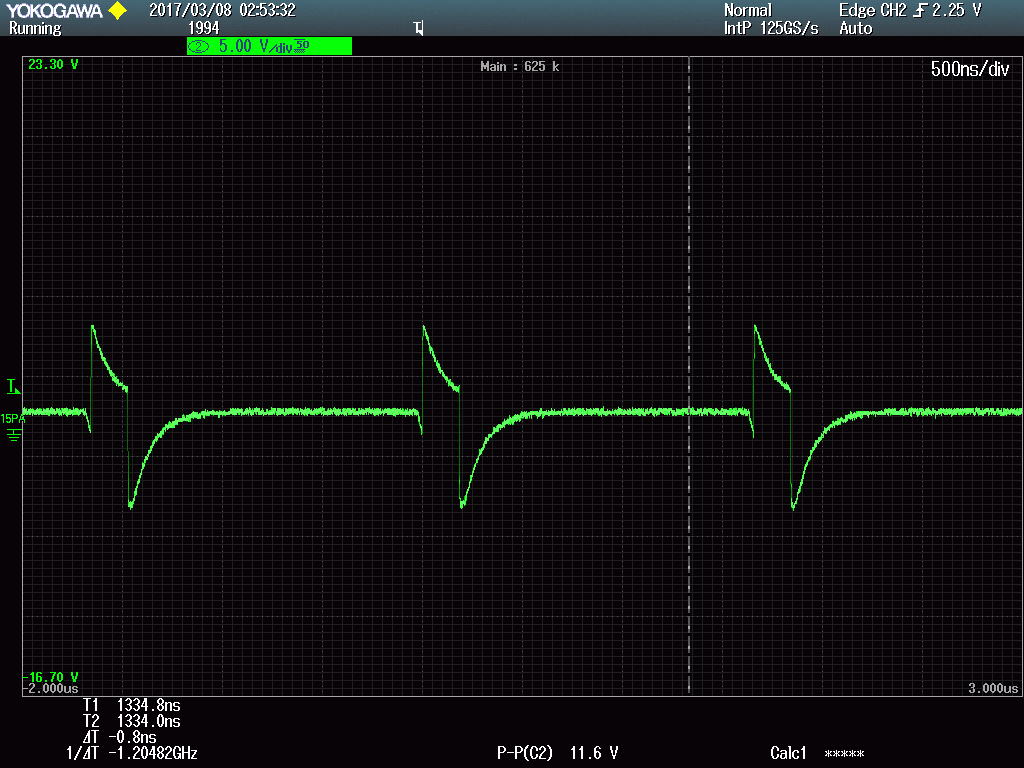

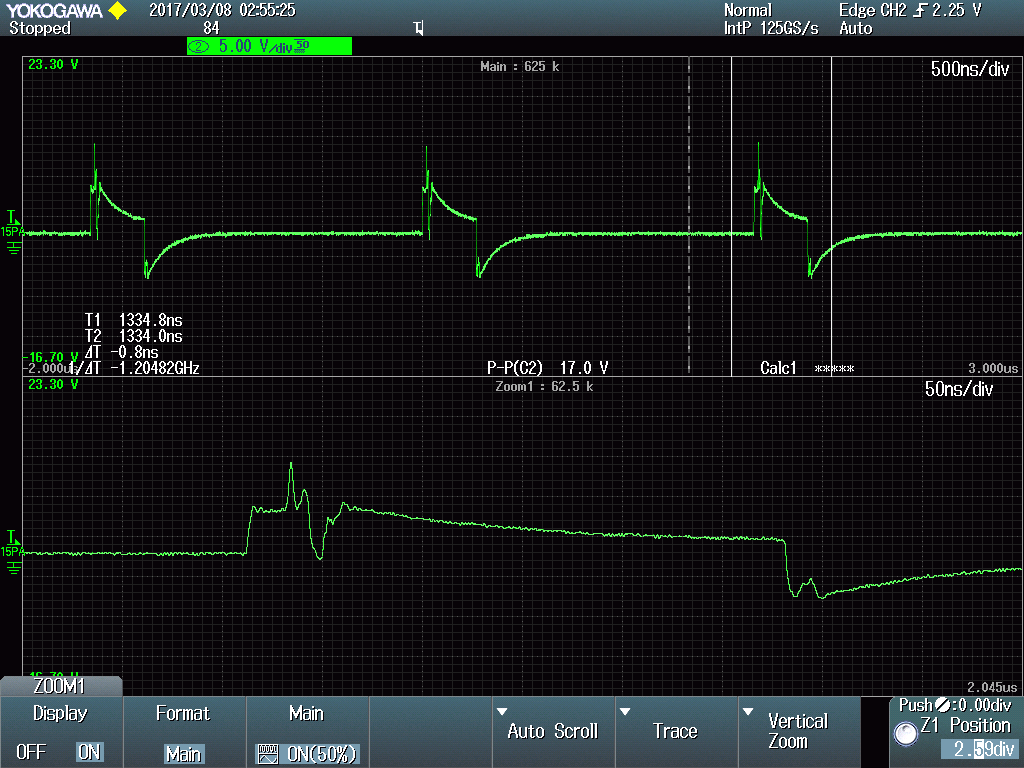

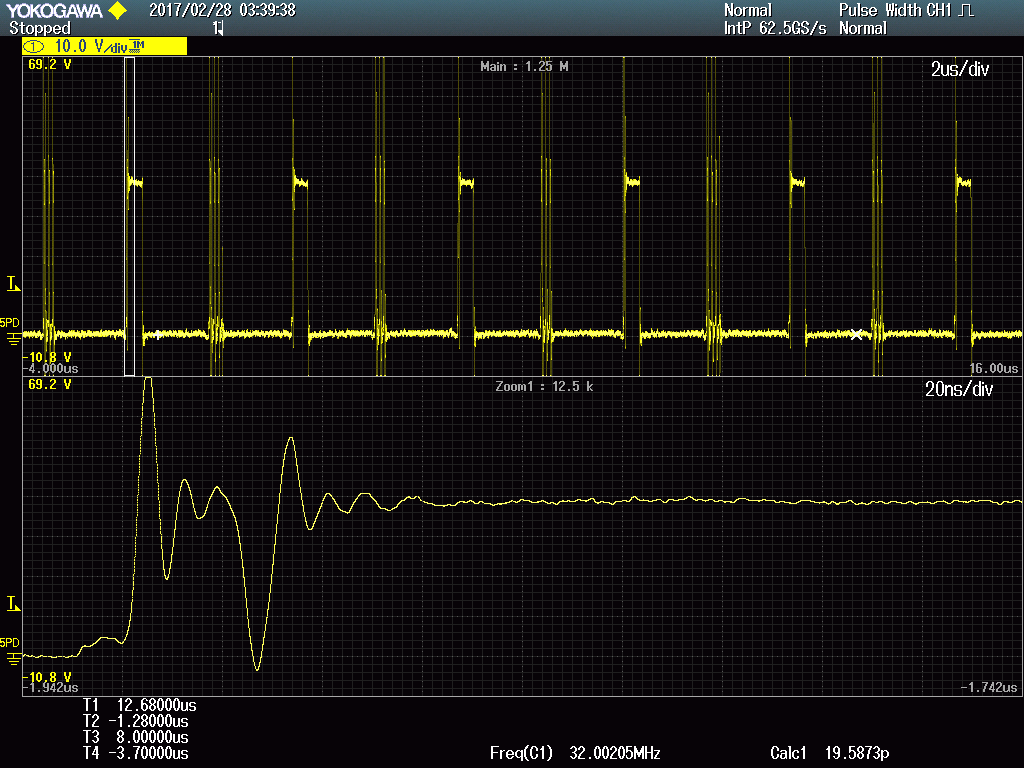

While searching for the reason, i came across a strange voltage dip in switch node voltage, which occurs just about 40ns after turn on of high side FET. This dip can be seen on high side gate drive signal as well. That confused me a bit, because it doesn't occered right at the rising edge of the switch node, but with some delay.

As ringing won't stops early enough this might be the reason for tripping the over current limit. (In threat TPS40170 blanking interval it is state to be 100ns) Thus the ringing approaches this point.

(Note over current limit is increased to Uilim = 300mV already)

Which pin of TPS40170 is susceptible to high dV/dt signals, that can actively pull the high gate low?

Sometimes it even results in some High Gate Drive oscillations within a whole Ton time. At low load conditions this doesn't occurs as dV/dt of switching node is much lower. (Due to negative inductor currents, switch node is ramped up from output inductor, and then switched on from FET. ) -> Can the high drive state be influenced by AGND bouncing or PGND bouncing?

The synchronous buck converter has following parameters.

Uin = 23V bis 44V

Uout = 5,1V

Iout = 5,5A

f = 600kHz

Best Regards,

Thomas