Hi,

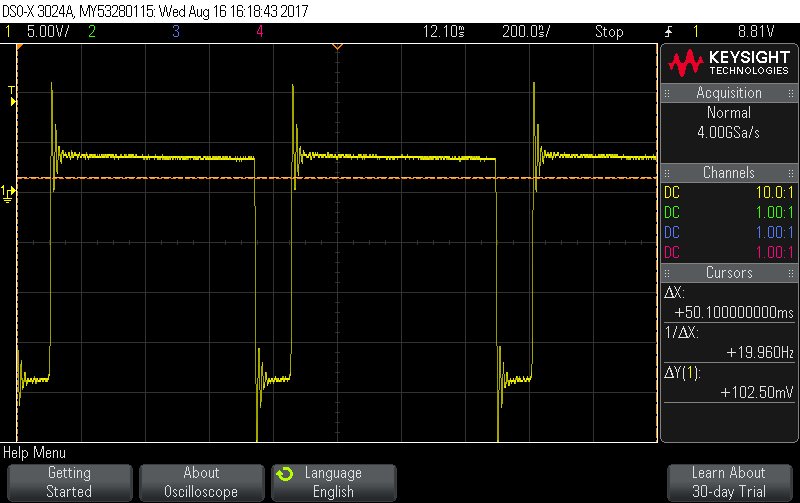

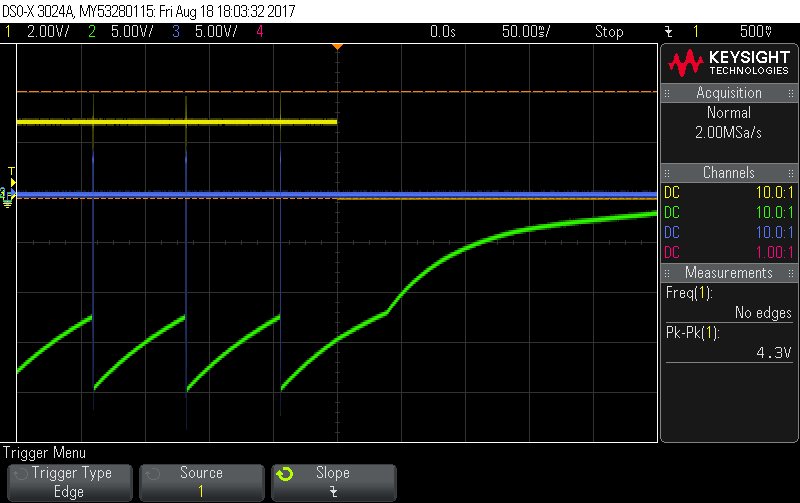

I have a problem with the negative output. Attached is the schematic (U79) and some pictures from the scope.

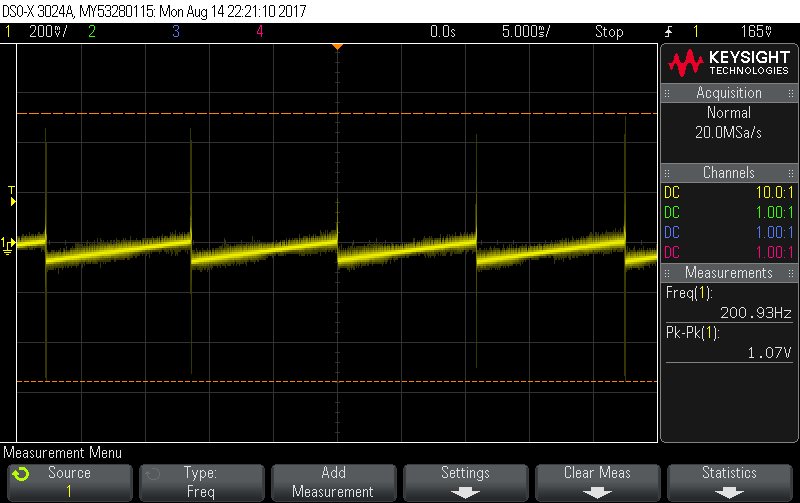

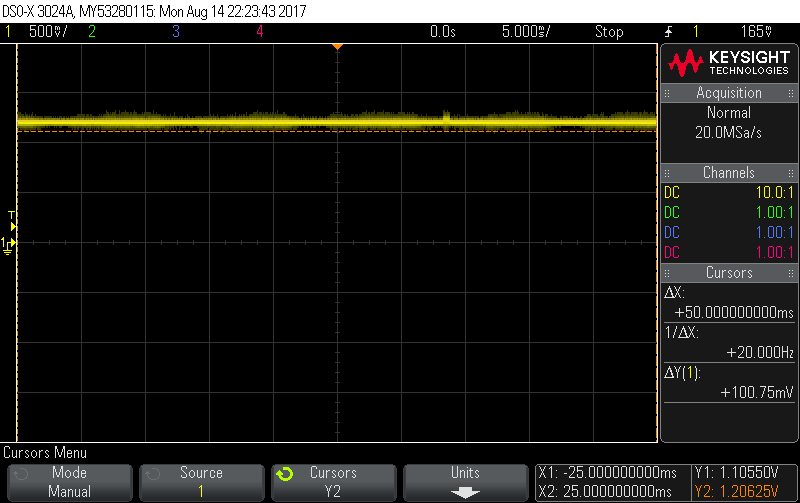

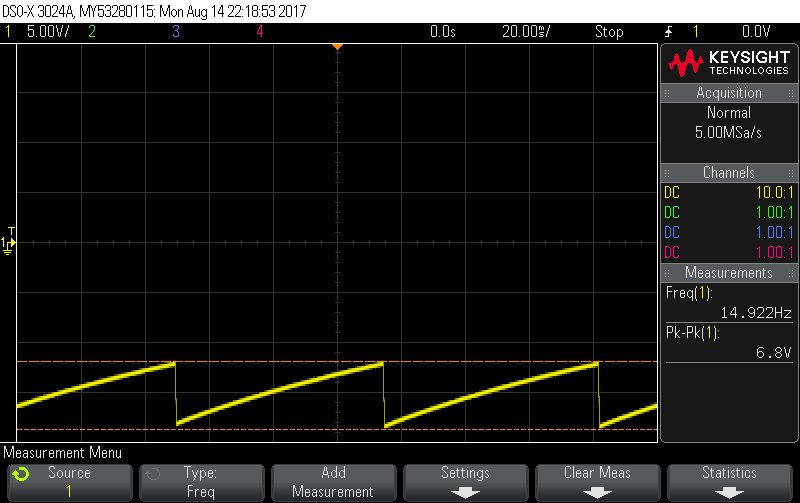

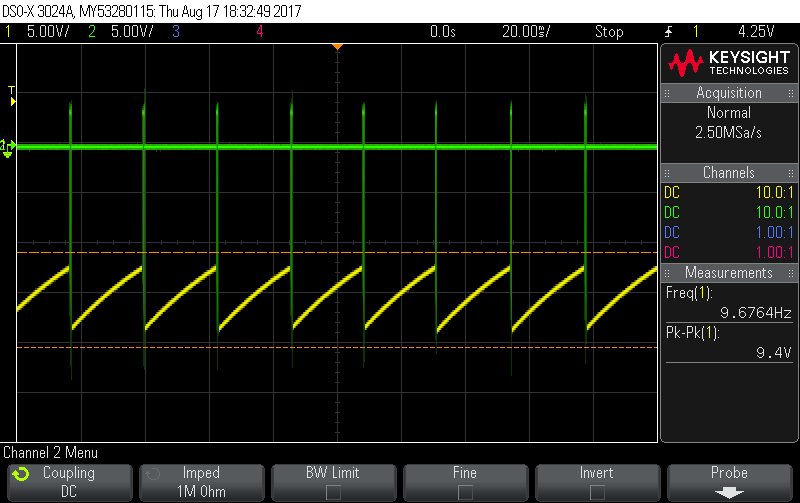

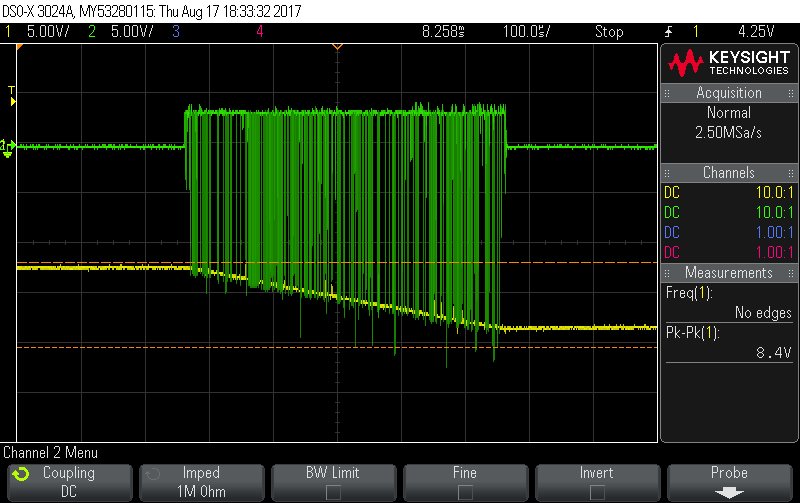

The scope results are with R2 = 100K and R4 = 100K as in the schematic.

Before that, by mistake, R2 was 75K giving a 18V at VPOS. So I replace it to the current value.

Is there a problem in the chip itself ?

Thanks

Noam

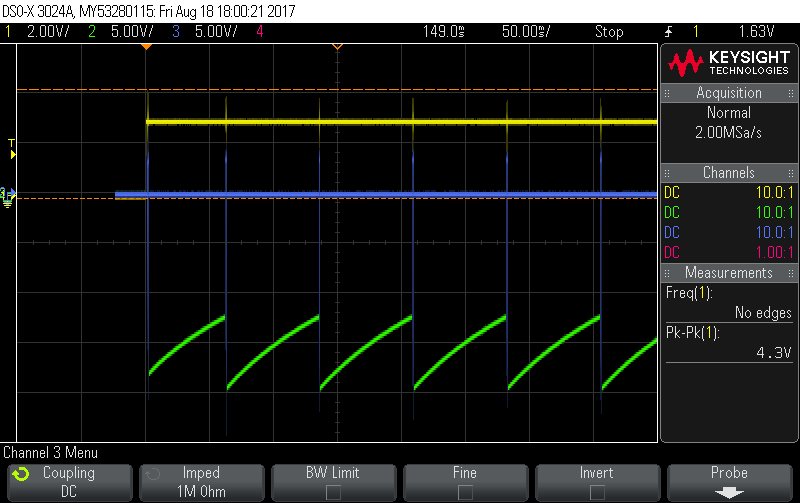

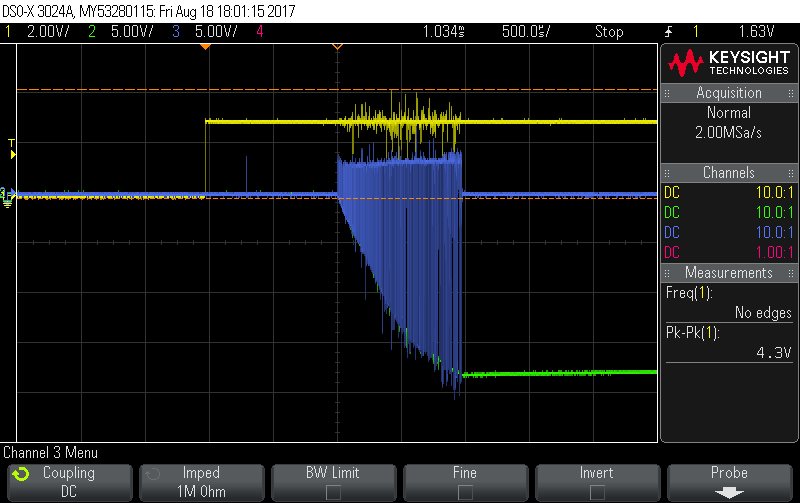

VREF

FBN

VOUT NEG