Other Parts Discussed in Thread: TINA-TI, TPS40170

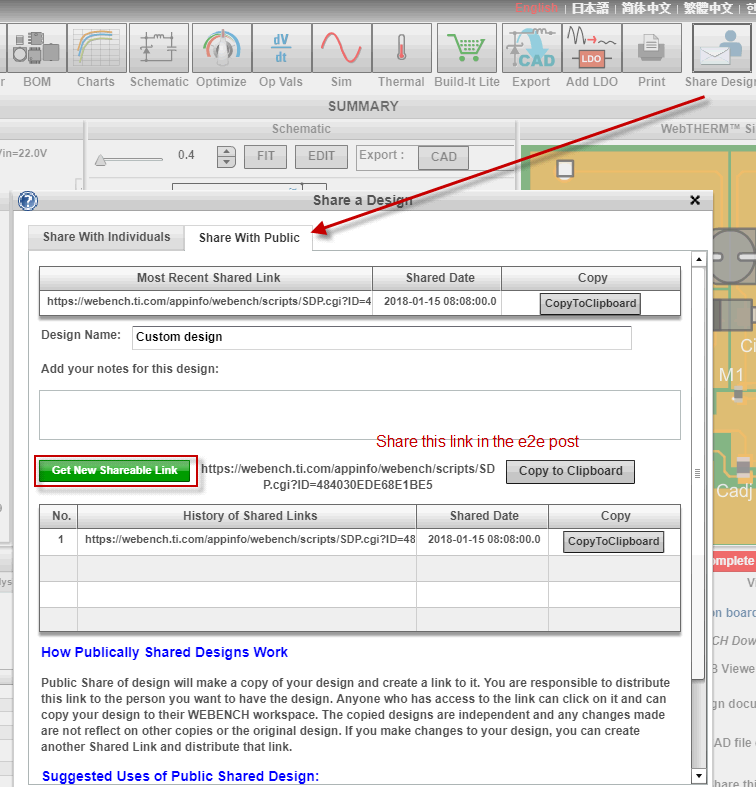

Tool/software: WEBENCH® Design Tools

Hi TI support,

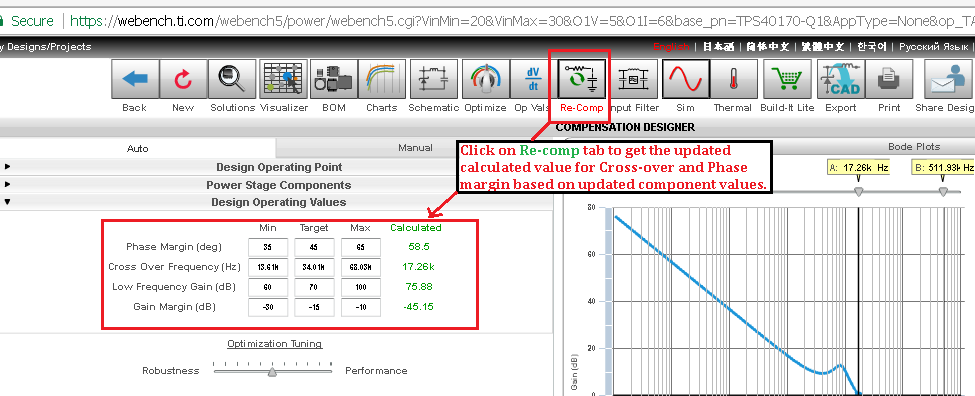

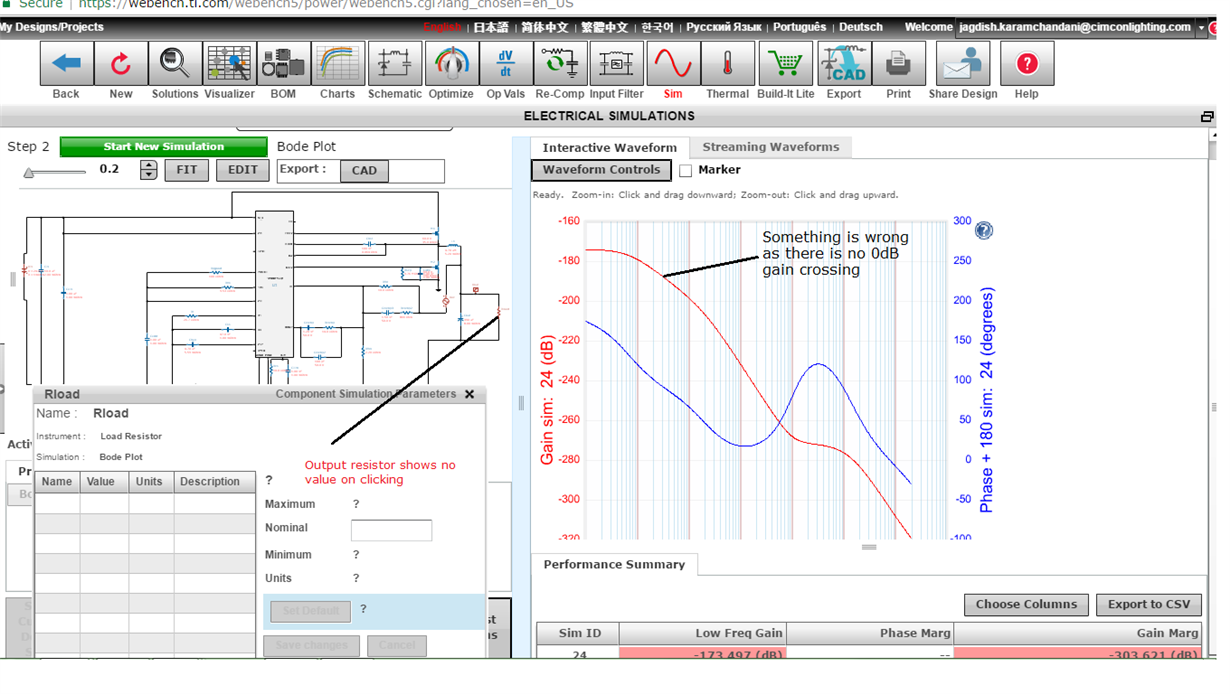

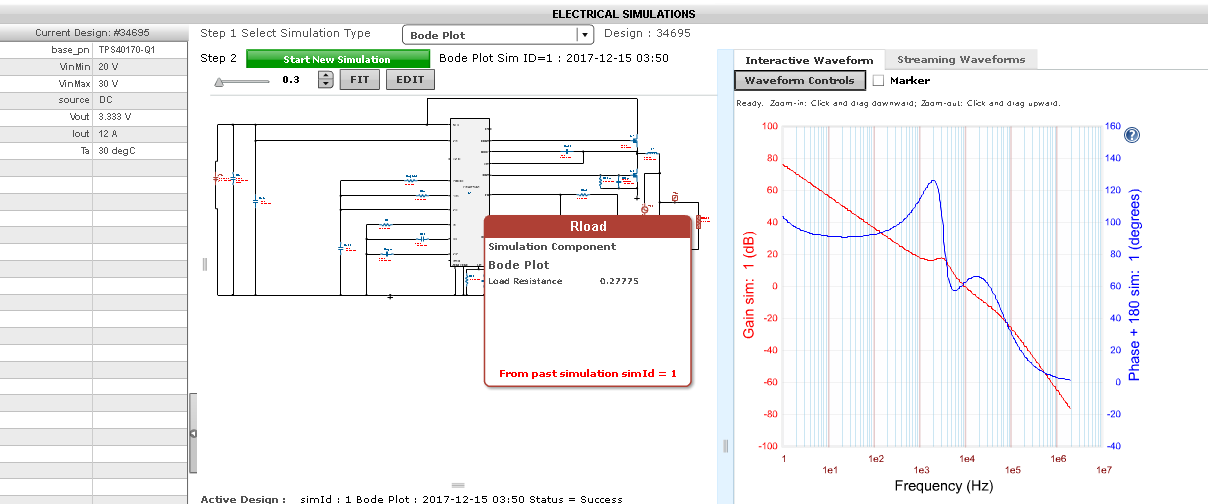

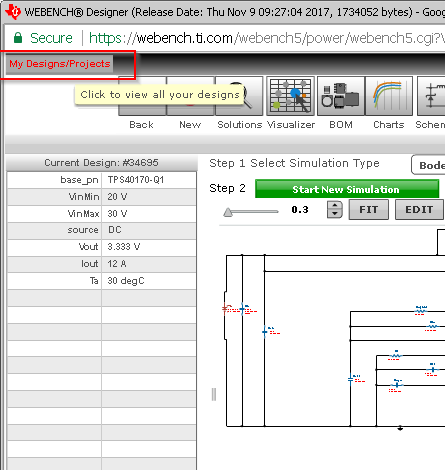

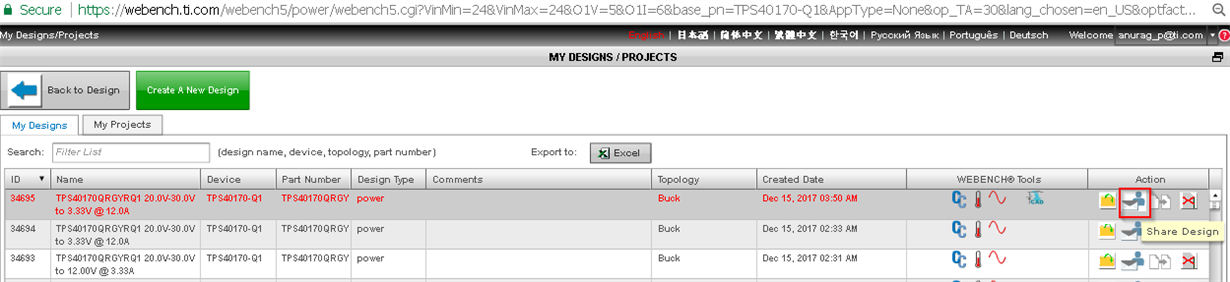

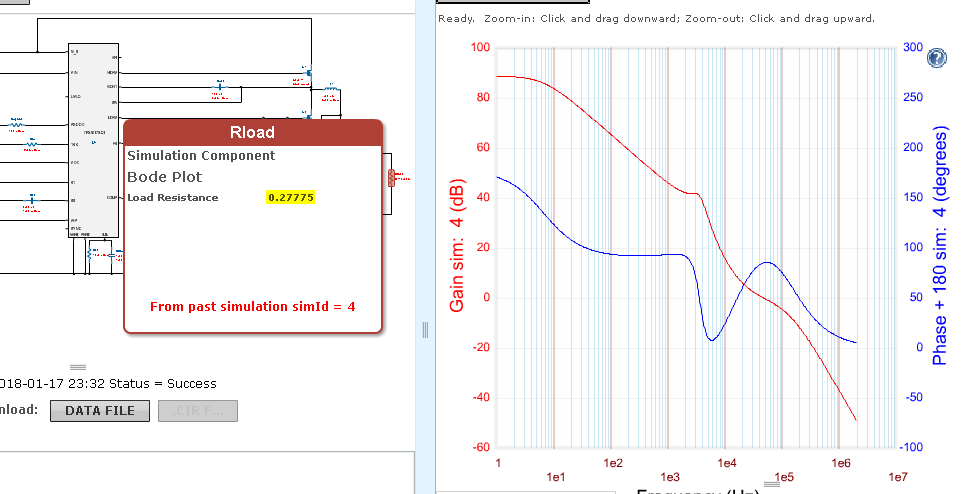

1. I generated 24V to 5V/ 6A design using Webench. Did customization of some components, used TPS40KType III tool for compensation network. Everything seems working fine with good phase margin in "Op Vals" but those things are not visible in bode plot simulation.

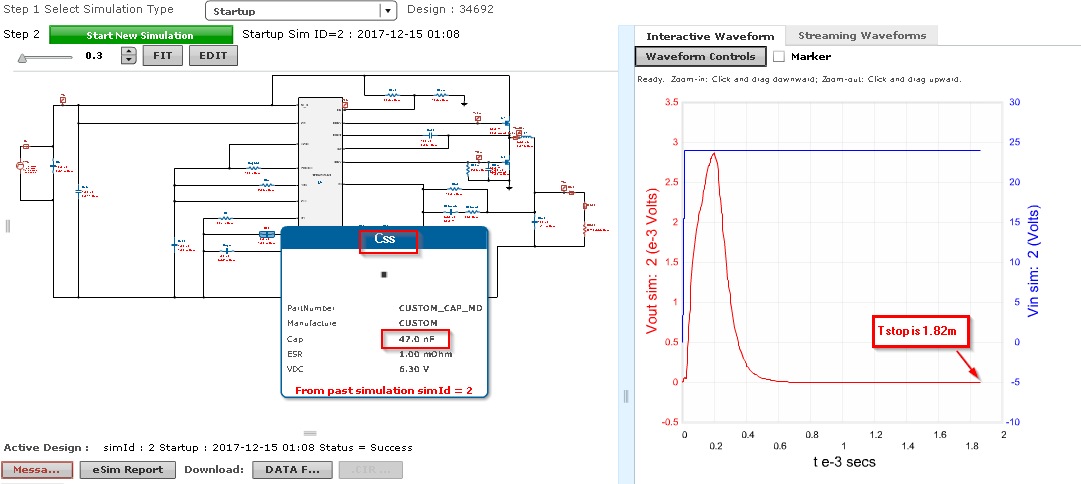

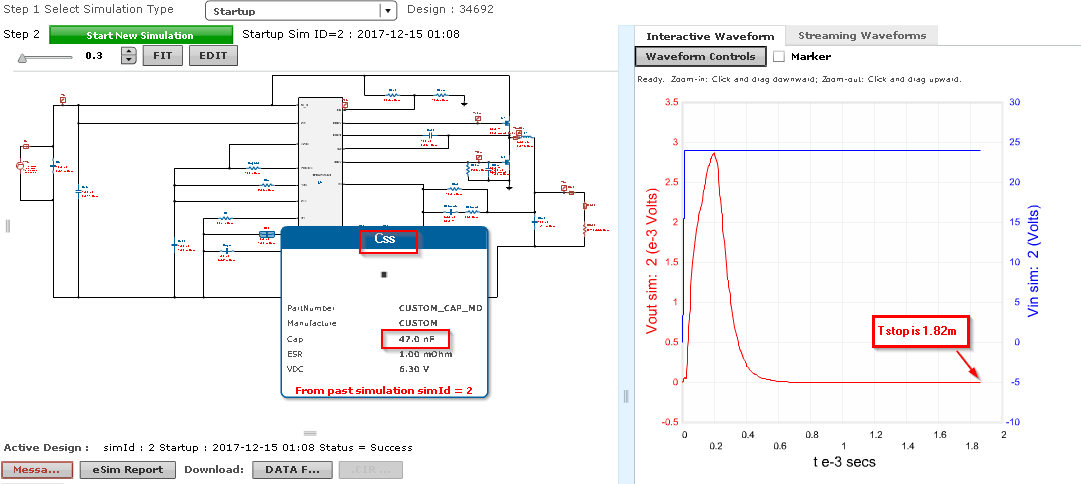

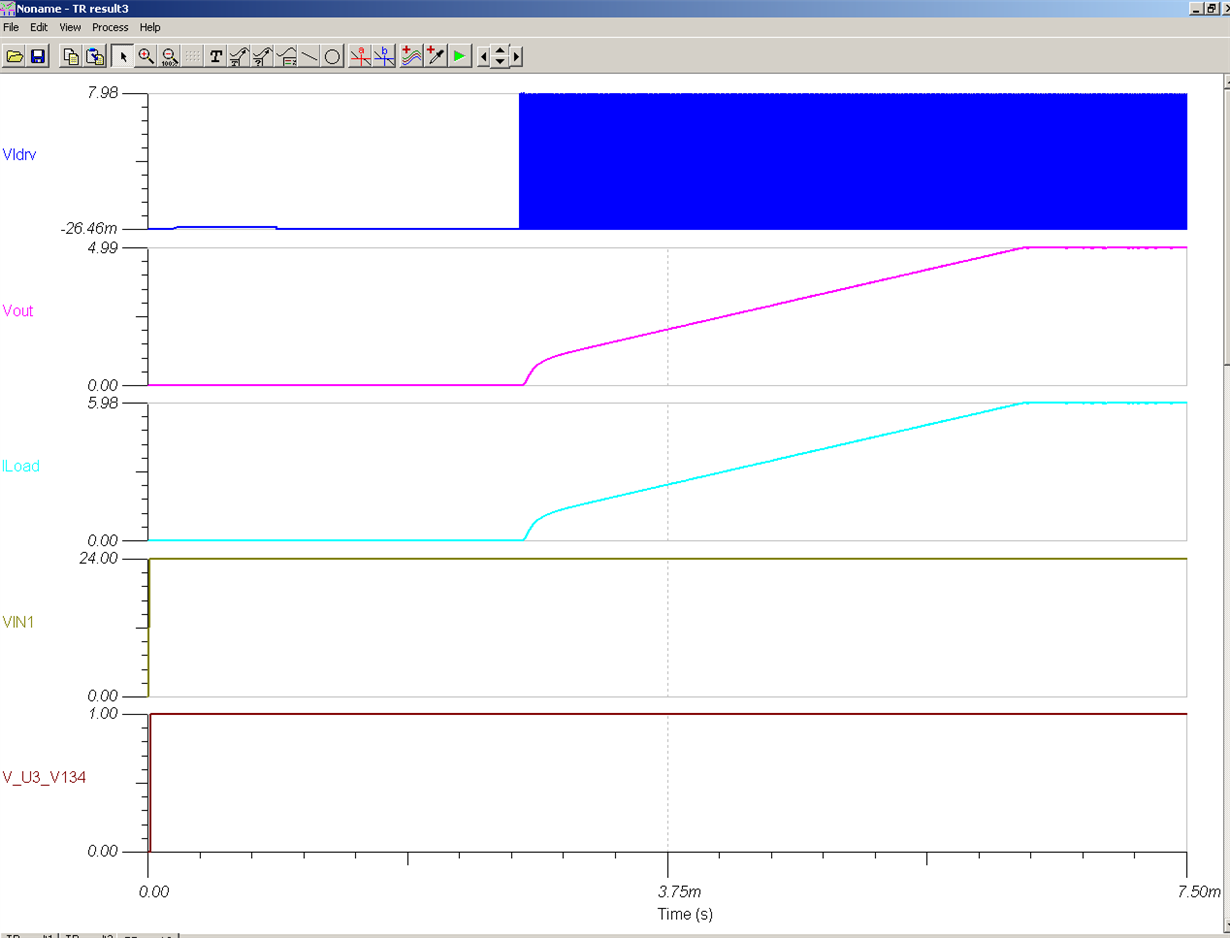

2. The other issue I face is startup simulation fails with Css=47nF. This value has been selected as per datasheet guidelines. If this value is changed to 2.2nF then startup simulation does work. Please find attached webench design generated along with this thread.

Thanks,,

jagdishwebench_design 24V-5V 6A.pdf