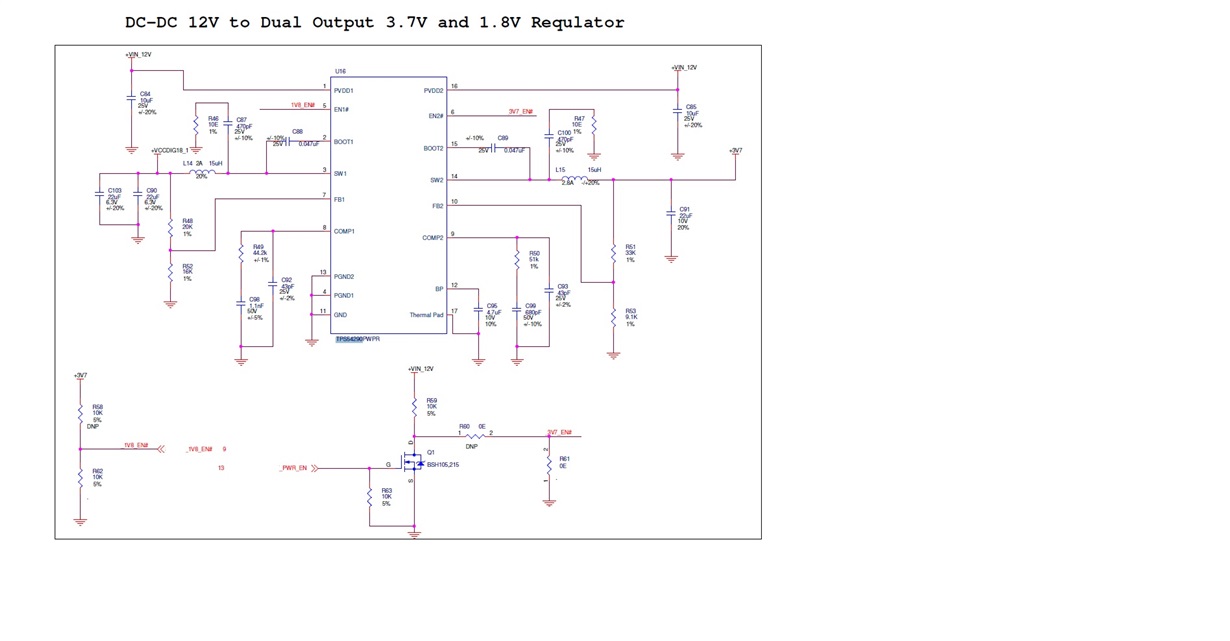

Hi, We are using TPS54290 in our design and using it as Dual output source ( 1.8V and 3.7V respectively) .

PVDD1 and PVDD2 are shorted and fed by 12V supply.

Default EN1 and EN2 are pulled down.

After turning on input PVDD1=PVDD2 = 12V . We are getting Out 1 around 1.48-1.9V on 5 boards we tested( should be 1.8V as R1 /R2 at FB1 are 20K/16K) .

But major issue issue is with Out 2 . we are getting around 1.77V - 2V range on 5 boards we tested. (should be 3.7V as R1 /R2 at FB2 are 33K/9.1K) .)

Is there any sequencing required for EN1 and En2 ( EN2 should come before EN1) in case when we have PVDD1 and PVDD2 tied together?