Hello,

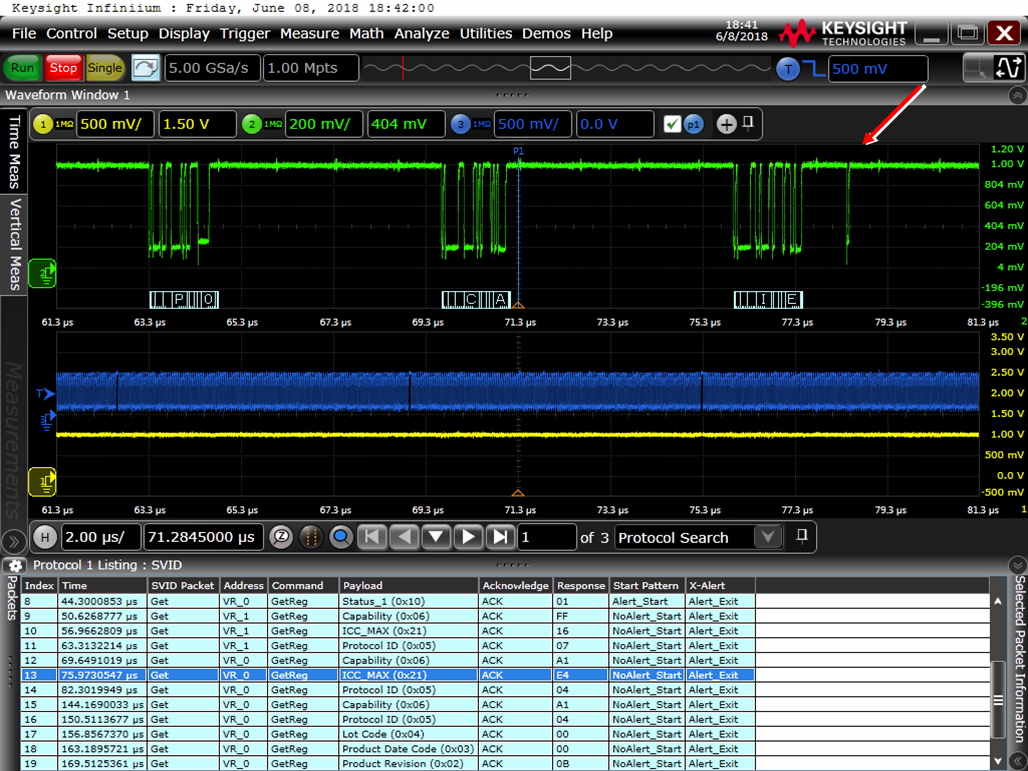

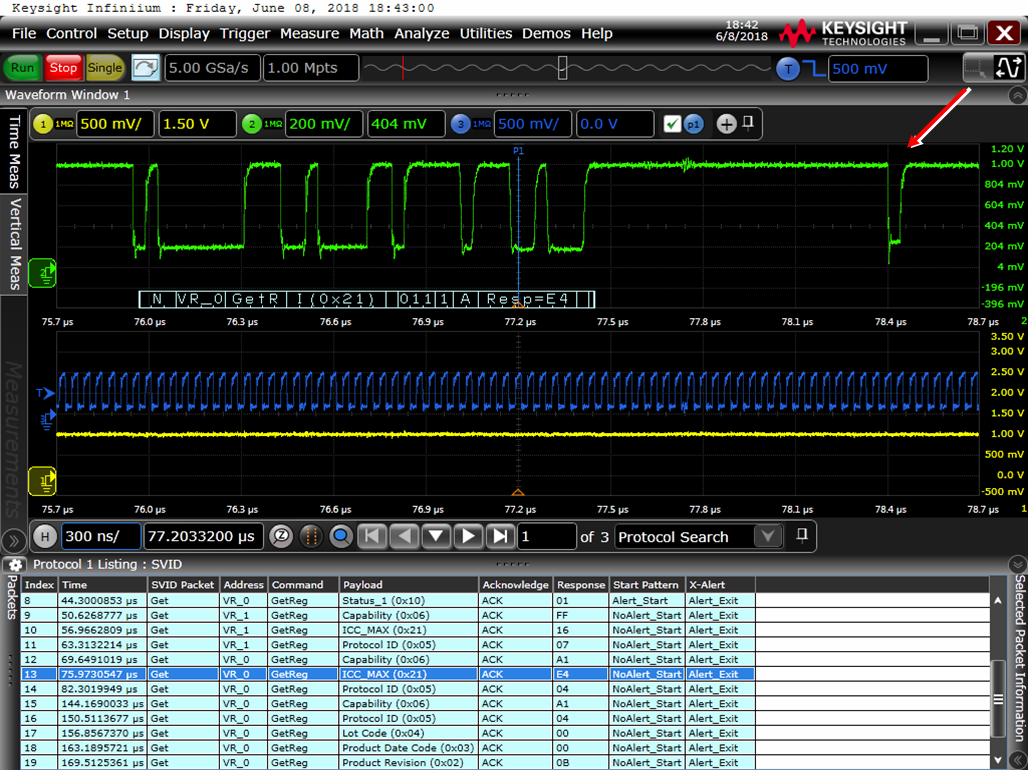

Have you ever seen the following ack(?) pulse from tps53622?

The details are as follows:

[environment]

Host : Intel Xeon

VR_0 (SVID addr 0) : another vendor's VR

VR_1 (SVID addr 1) : TI TPS53622

[issue]

This issue occurs every power-on sequence.

The pulse appears at the same timing.

At the moment, it seems that the pulse is from tps53622.

The reason is as follows:

- the low-voltge-level is as same as tps53622. (not same as VR_0)

- it does not appear, when tps53622 is disabled. (set svid addr 0xF by Fusion Digital Power Designer)

Is there anything for me to confirm?

Thanks,