Hello,

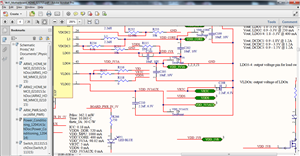

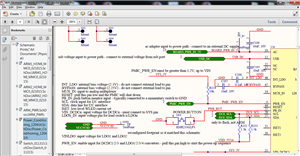

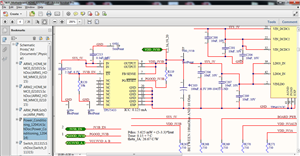

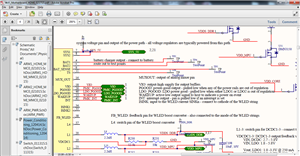

I have a question about the operation of the TPS65217C PMIC. From what I have gathered, the device immediately powers up the LDO1 rail, which is used for the VRTC voltage when interfacing to the AM335x series. The SYS_5V also immediately is connected to the input power. The VRTC rail controls the RTC_PORZn pin of the AM335x processor, which then starts the power-up sequence of the processor. After the RTC stabilizes, the processor launches the rest of the power-up process by activating the PMIC_POWER_EN signal.

From reading the datasheet, it appears that the default operating condition for the other 3 LDOs as well as the 3 switcher outputs is in the off state. I2C is required to enable these signals, but the peripherals of the AM335x require voltage from one of the outputs that is disabled, so it seems to me that there is a chicken and the egg situation there. I'm sure I am interpreting something incorrectly and would appreciate a detailed response on how the power-up is handled.

To attempt to test this device prior to using it on a much larger design, I made a PCB with the reference design on the Beagle Bone Black board (minus the AM335x processor) and tried to test the IC. Upon powering on, the SYS_5V oscillates between 3.11 and 4.0 V, the current draw ranges from 1 mA to occasional spurts at 12 mA and the LDO1 rail oscillates between 0V 0.33V and 0.65V. I'm not really sure what to make of this. It seems that the only input that the power-up is reliant on the is the PMIC_POWER_EN, so it seems like tying it high would cause the system to power up.

Could you please enlighten me on my mis-interpretations and oversights?

Thanks.