Hi,

Can anyone help to resolve the start up time issue of TPS65051RSMT.

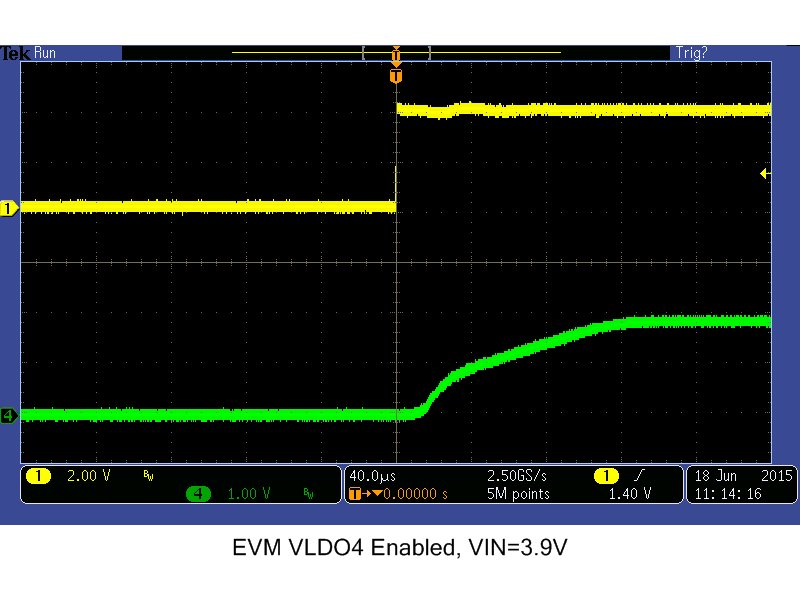

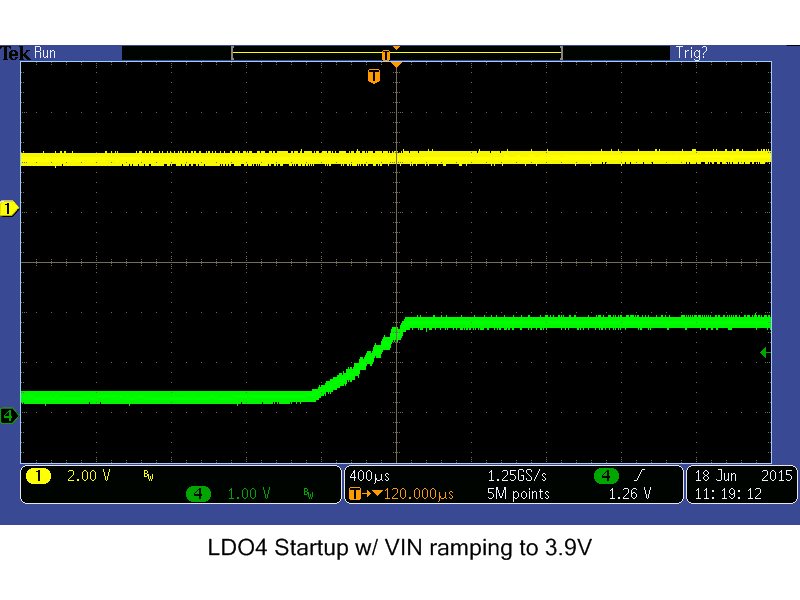

As per the datasheet the maximum start up time for the LDO's is120uSec.But measured value is 12mS.

Please find attached file's for wave forms and schematics and let us know if any modifications required.

Rgds,

UmaMahesh