Other Parts Discussed in Thread: TPS653850-Q1,

Please let me know about three points below for TPS65381-Q1 (and TPS653850-Q1).

①I think that BIST function begin after VDD6 rail ramps, is it correct?

If any other condition for BIST begin, please let me know.

(Isn't BIST function from the beginning? )

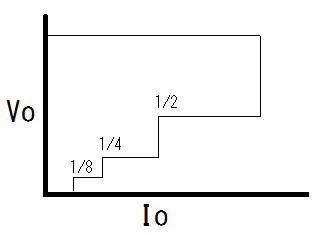

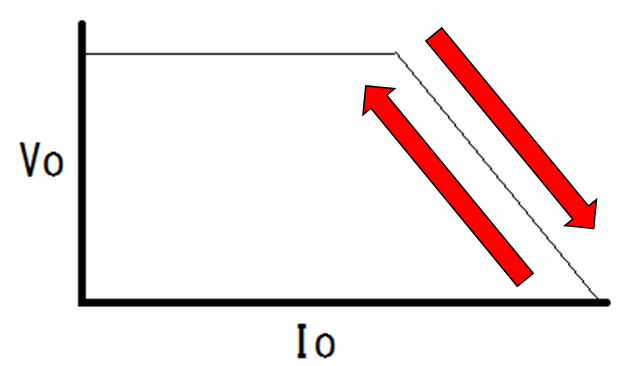

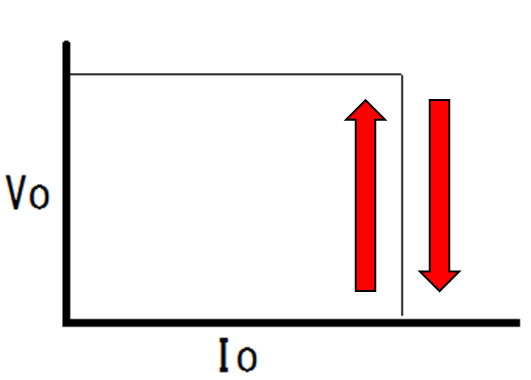

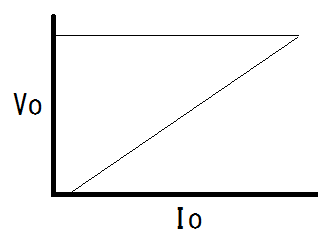

②Which is the TPS65381-Q1's overcurrent protection below?

③About the above question ① and ②, is TPS653850-Q1 the same function (answer)?

Best regards,

Satoshi

No.4

No.4