Hi,

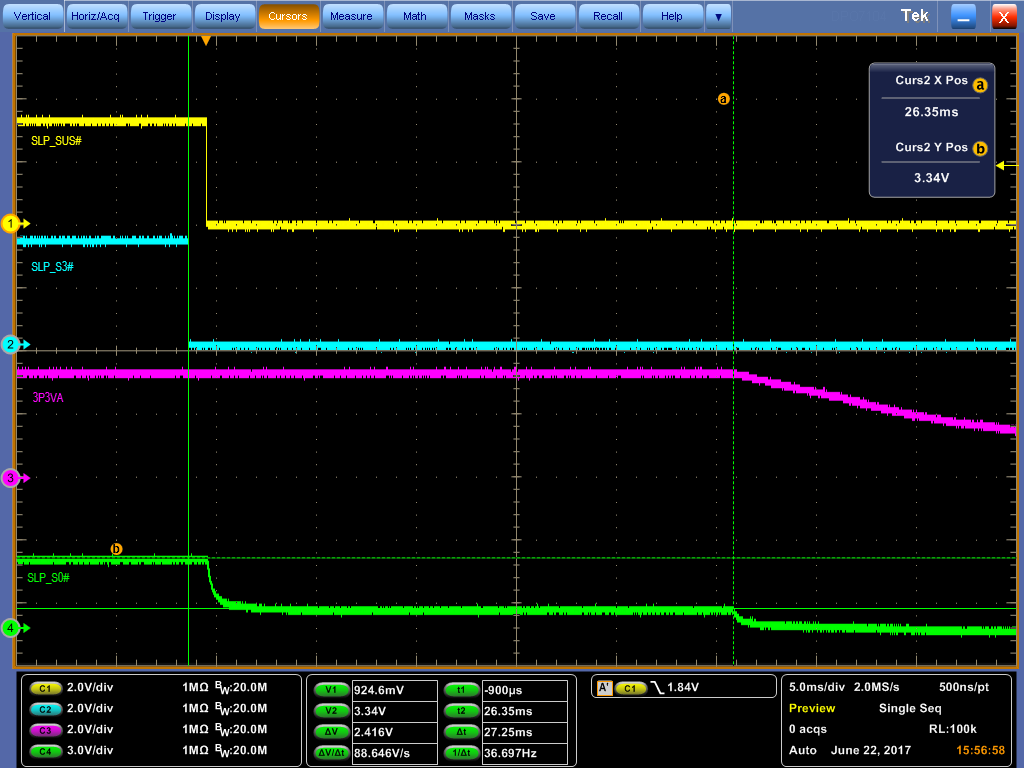

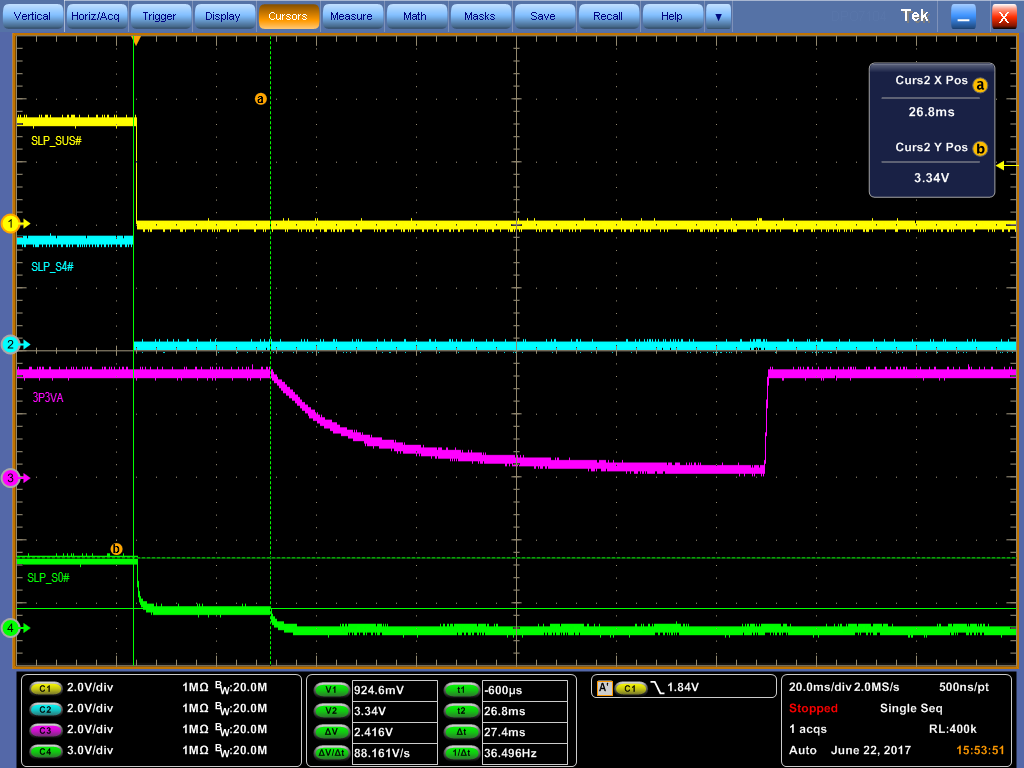

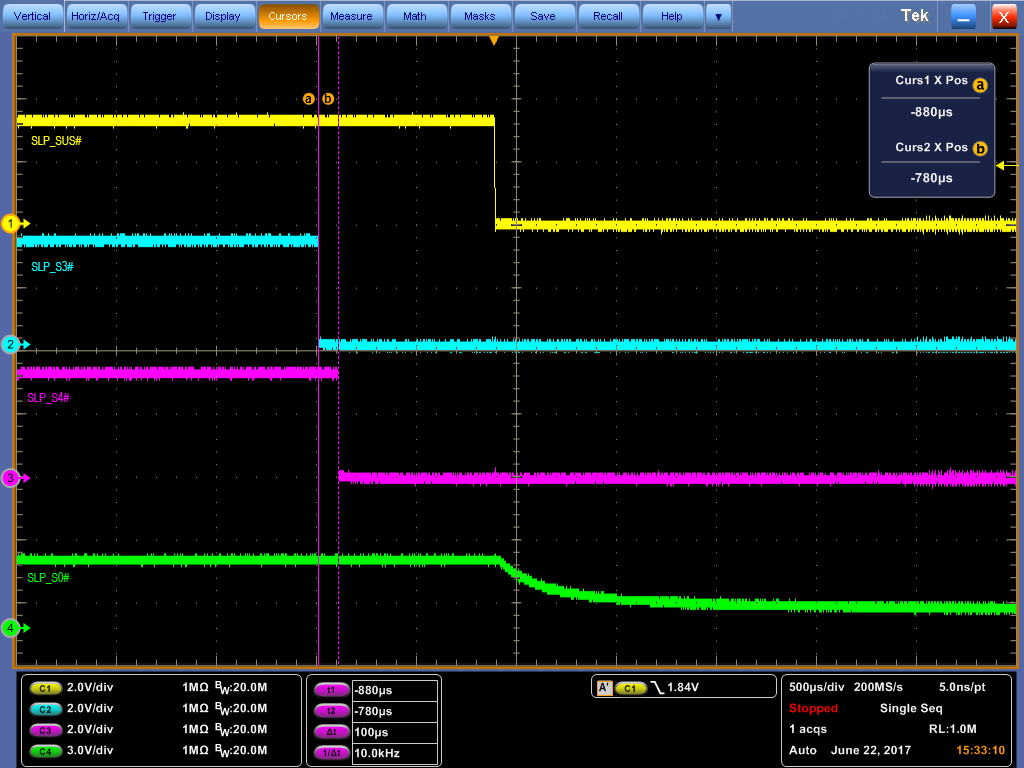

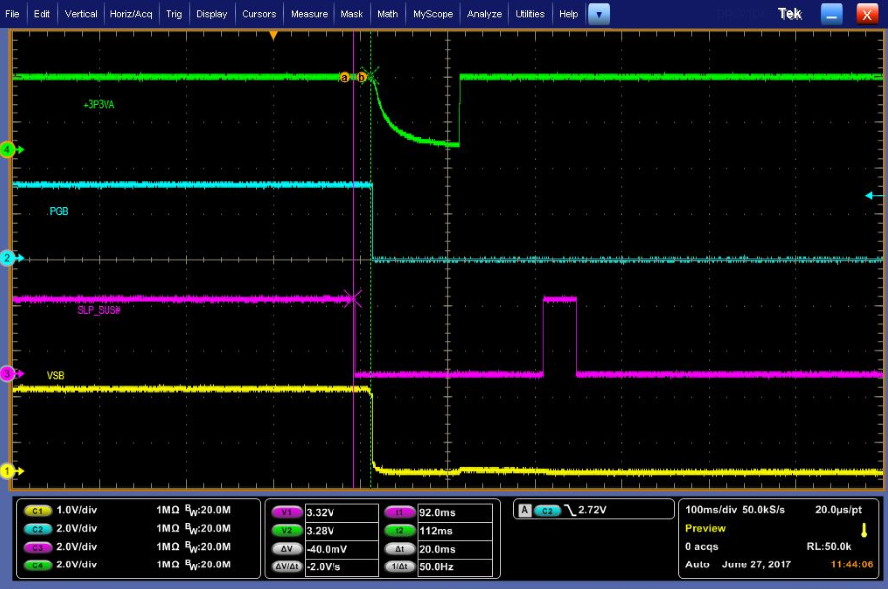

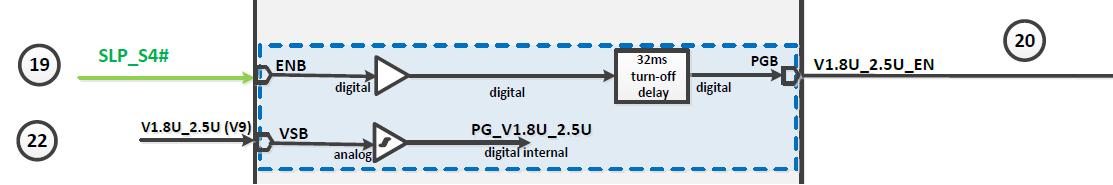

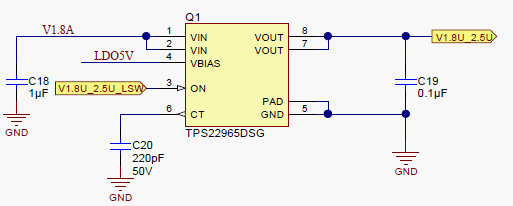

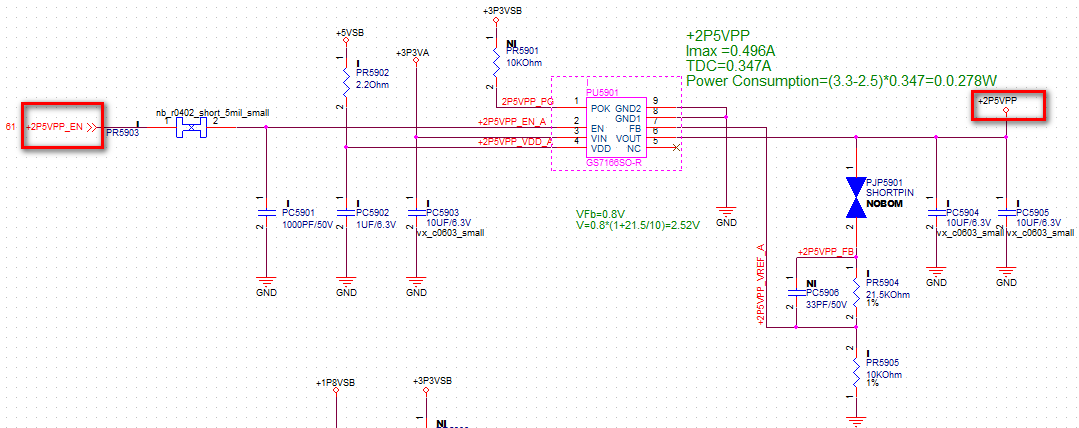

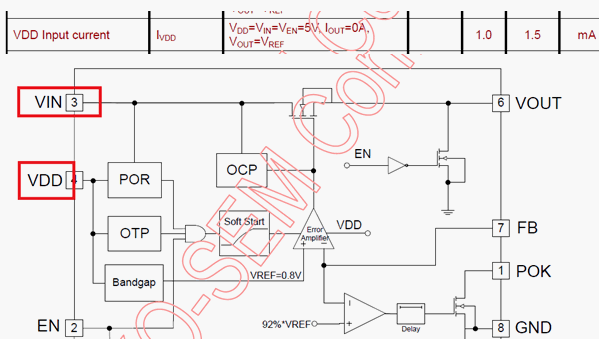

Customer found VR3 is unexpected turned off while system enter DEEP SLEEP S4/S5 mode, and be turned on automatically some time later. Related waveform w hile it enter sleep mode is as below. May i have your comments why VR3 is turned off at this moment?

Thanks!

Antony