HI:

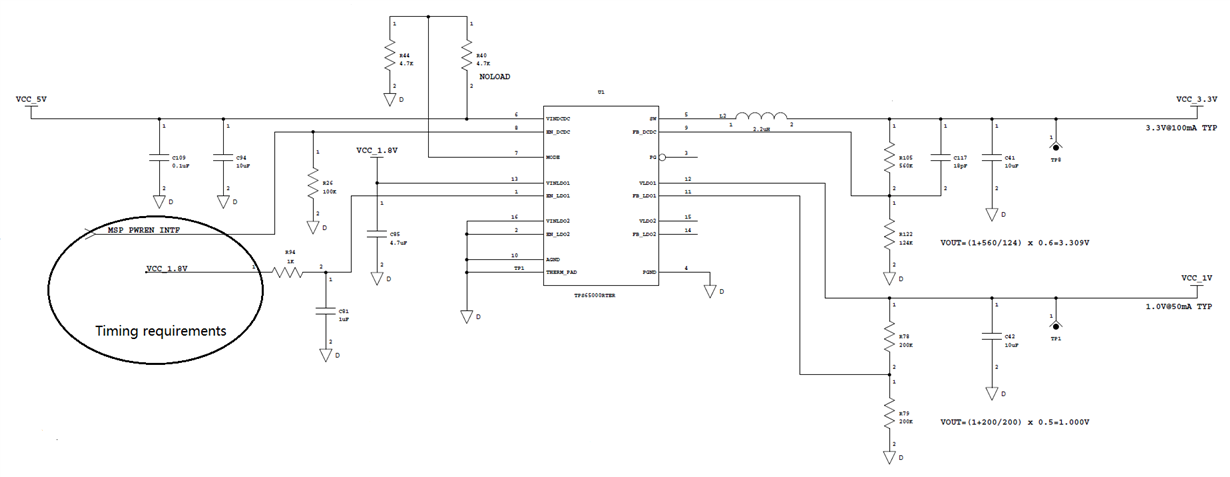

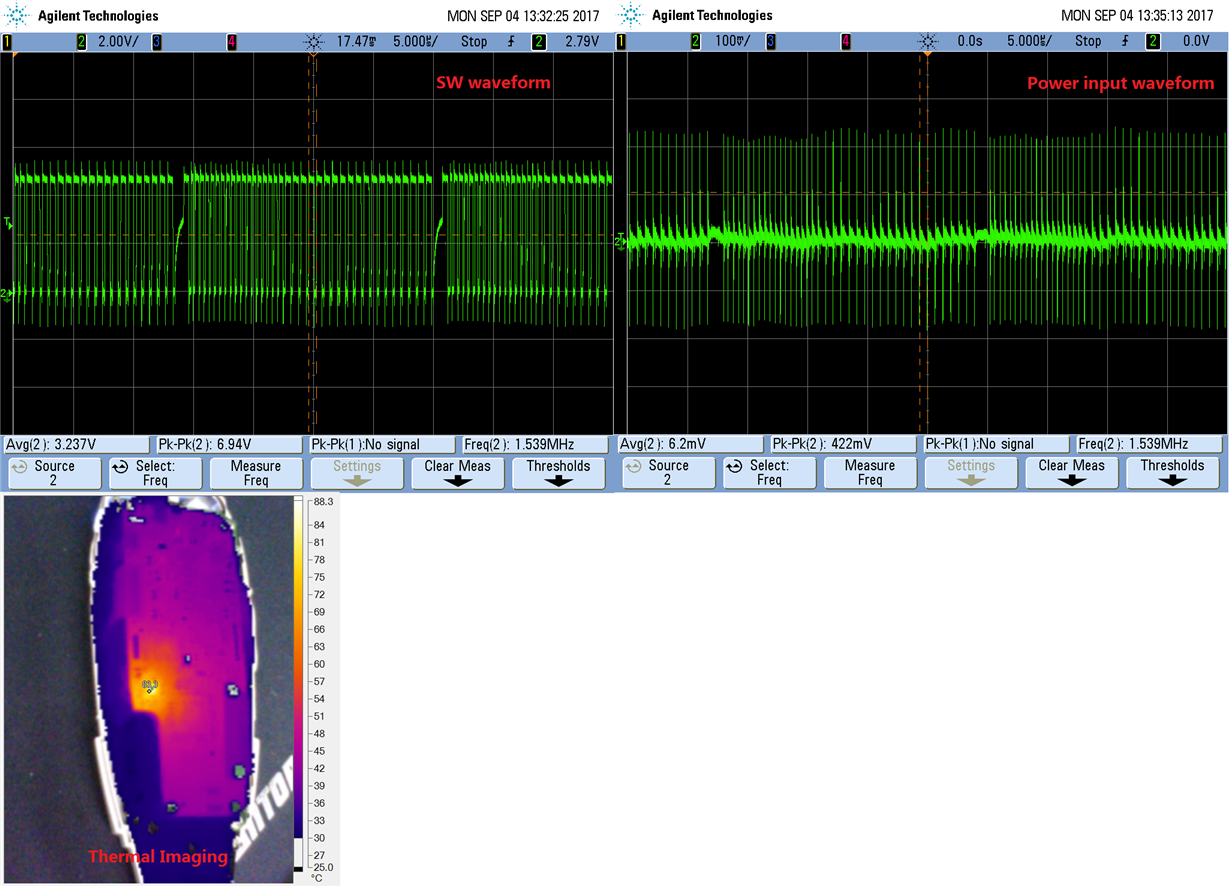

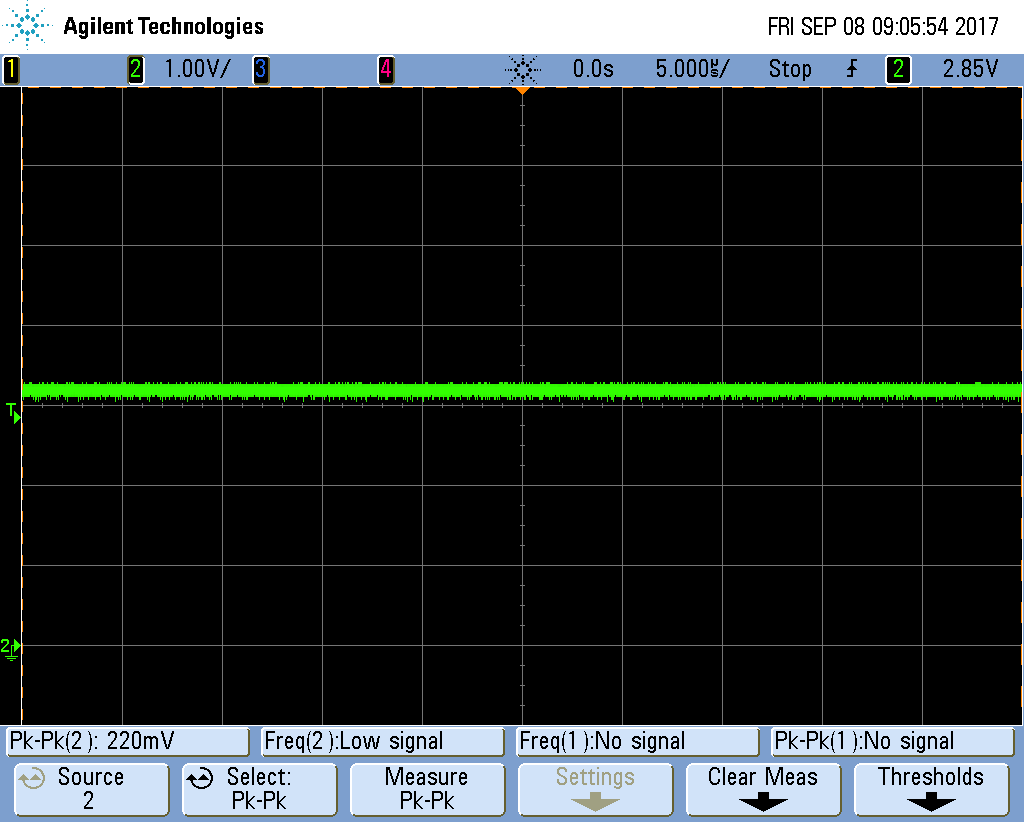

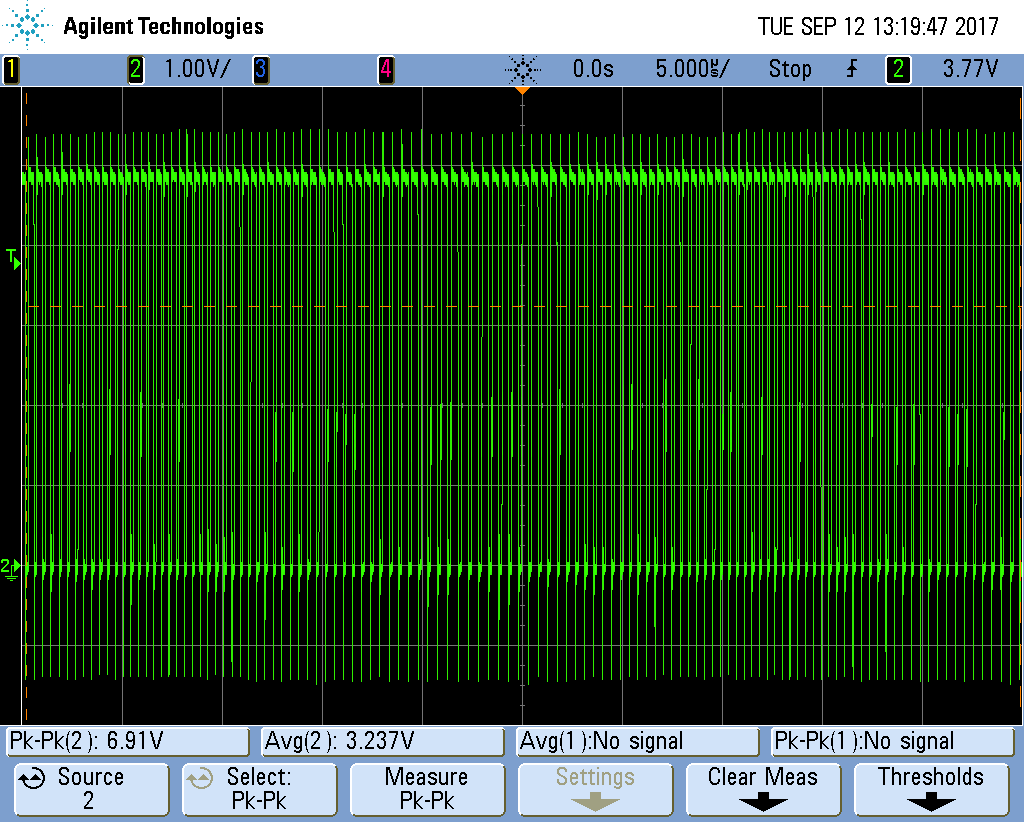

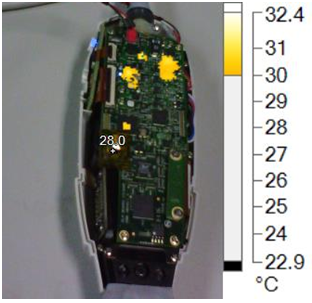

Our products use the TPS65000RTER as the system power supply, from the product development stage to the final mass production stage, often encountered the chip damage situation(More than a hundred samples), the abnormal phenomenon is the chip fever, but the output voltage is still relatively normal, it is difficult to detect, but when the chip heat to a certain extent will affect the system other part of the work, the chip around the schematic diagram see annex, please help analyze the cause of the chip damage, thank you.