Hi,

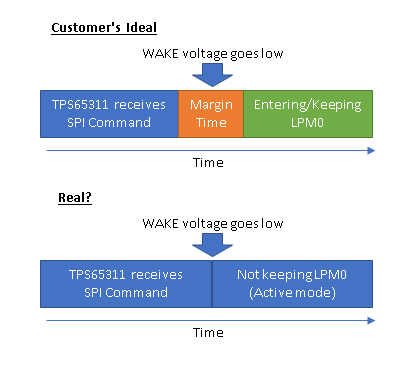

On my customer's system, the WAKE voltage goes low when power off by entering LPM0 mode.

So the TPS65311 can't keep LPM0 mode because WAKE voltage goes low after entering LPM0 mode.

They hope that there is some margin time from SPI command(to enter LPM0) to accepting WAKE voltage as below image.

Because they are considering that the device can keep LPM0 mode by precipitating forward WAKE LOW.

Is there such margin time?

Is their idea practical? (I think it is not...)

Please let me know if you have any question.

Best Regards,

Kuramochi