Other Parts Discussed in Thread: AM3358, USB2ANY, TMDSSK3358, TMP112

Team,

Please see below customer question:

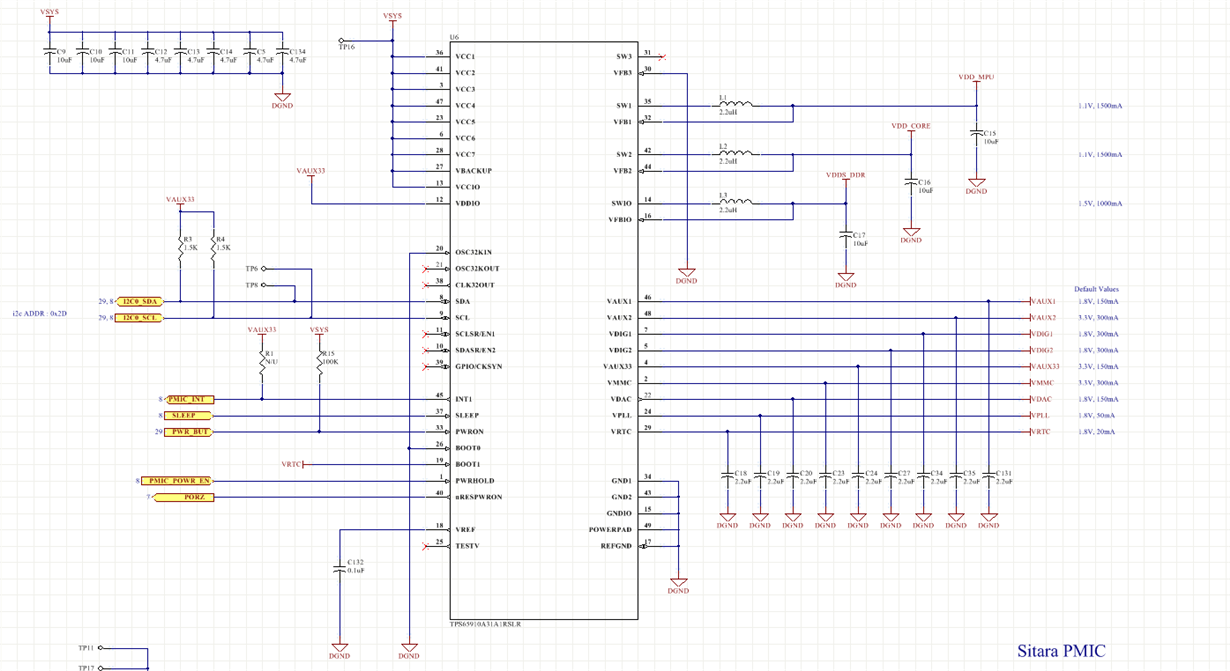

We are using the AM3358 (Z1) with the TPS65910A31A1 PMIC spec’d in. Our CM substituted TPS65910A3A1 parts.The datasheet doesn’t state the differences. Can you describe if they can be substitutes?

Also, we are experiencing a series of failures where the AM3358 seems to lock up and a PMIC reset (long power button press) doesn’t reset the micro.

I have looked at two of our assembled units which are exhibiting this problem. In both the PMIC is producing VDD_MPU = 1.1, VDD_CORE = 1.1, VDDS_DDR = 0.

If we completely remove power the PMIC will be reset and the units will reboot.

This problem state is spurious and difficult to repeat. Getting the same unit to repeat the failure mode hasn’t worked reliably.

Please ask your factory if they have ever encountered this problem and if the substitute PMIC could be the problem. If it isn’t the problem, see if they have any ideas. We are scheduled to launch the product next week, but this could be a show stopper.