Other Parts Discussed in Thread: DRA756, DRA75, TDA2

Hi,

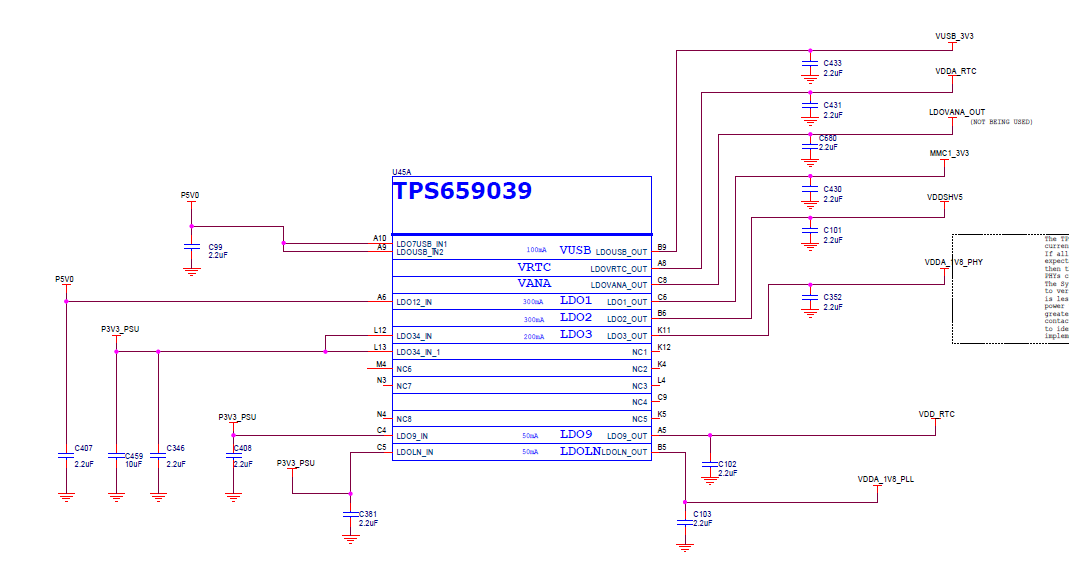

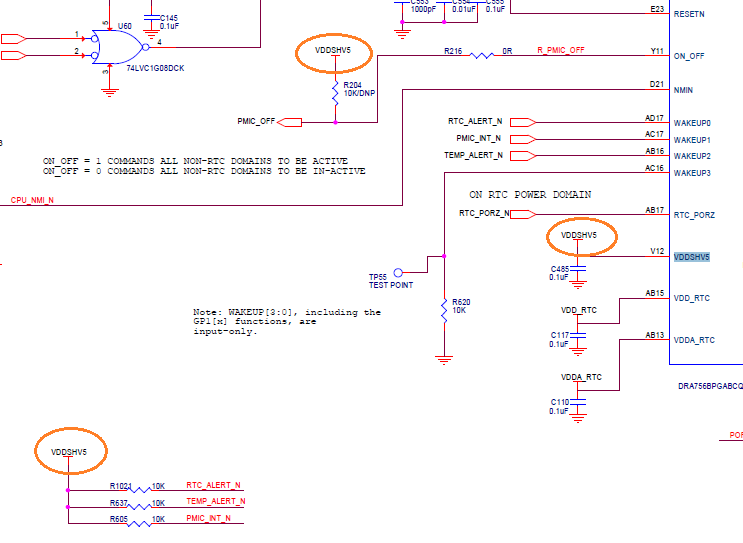

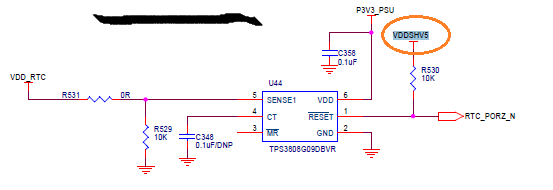

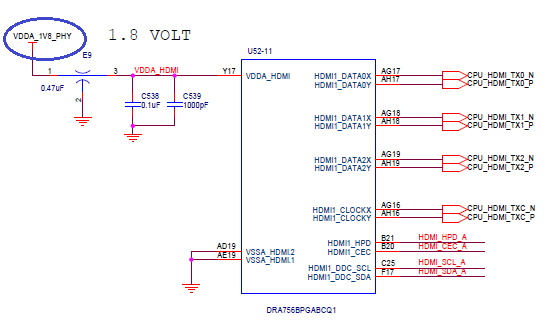

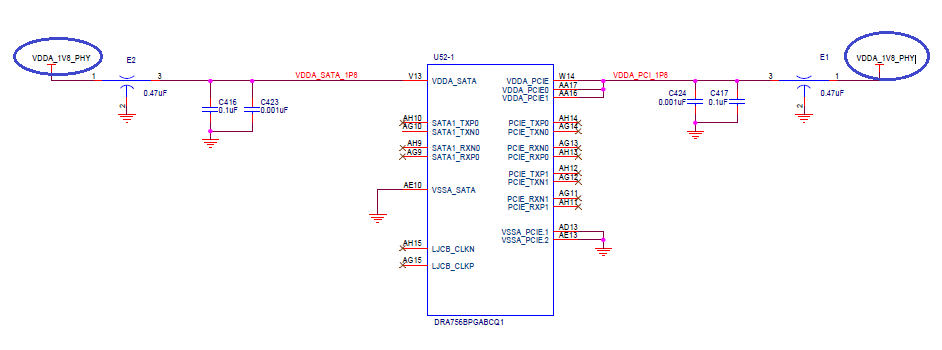

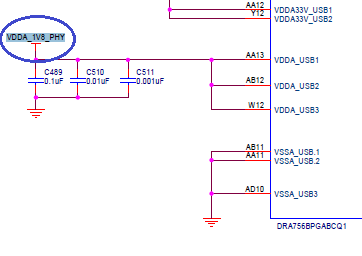

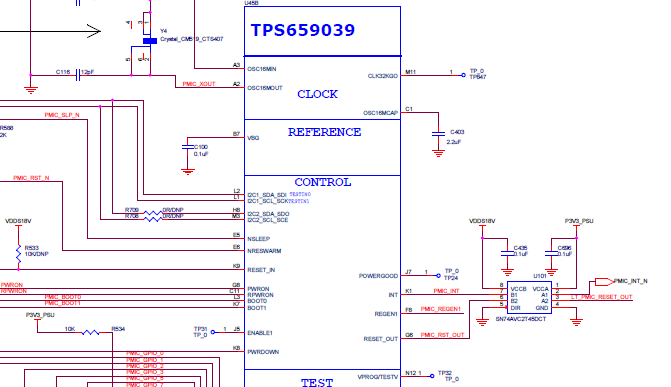

We are using TPS659039 for DRA756 power and we see that all the power sequencing is as per recommendation in datasheet.

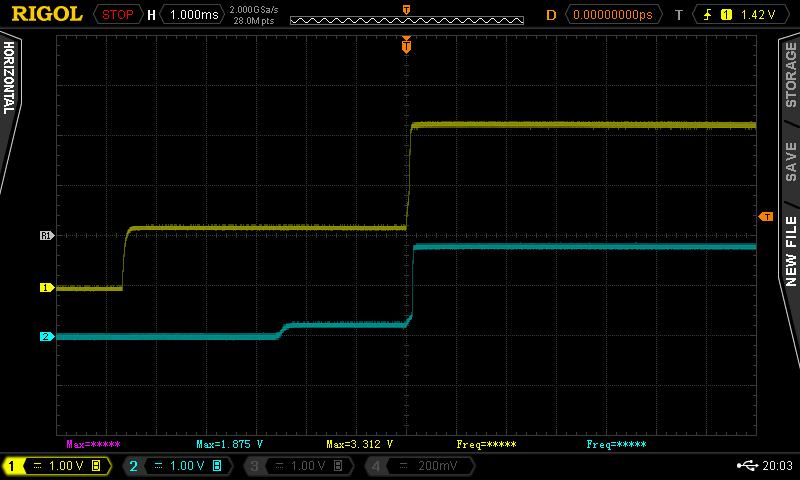

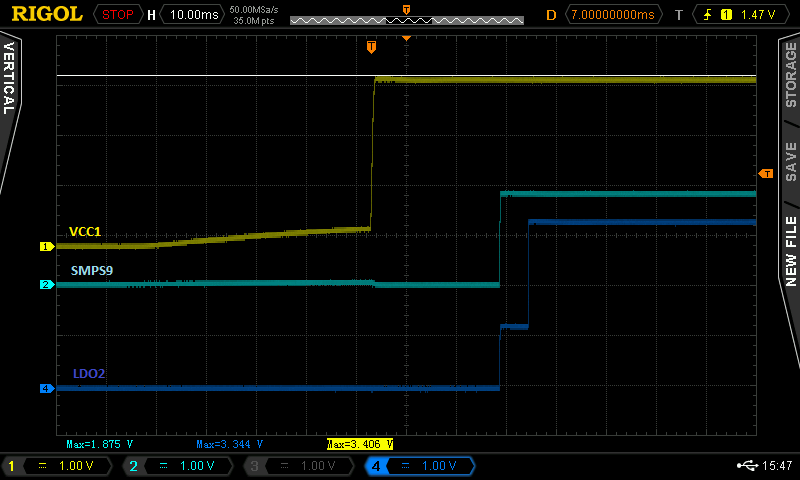

But for LDO3 and LDO2 we see unusual raising with some glitch.

As per my knowledge we have followed all design rules recommended by TI for TPS659039. Attaching the oscilloscope capture for LDO3 and LDO2 power. Please guide us what could cause this issue and how can we resolve it?

Note: Channel 1 - LDO2, Channel 2- LDO3

Regards

Bharati