Hello,

I have some questions about LM5060-Q1.

1.Please let me know the guarantee tolerance dose of the body Diode of SENSE, nPGD, UVLO, and an OVP pin.

Both of forward current and backword current.

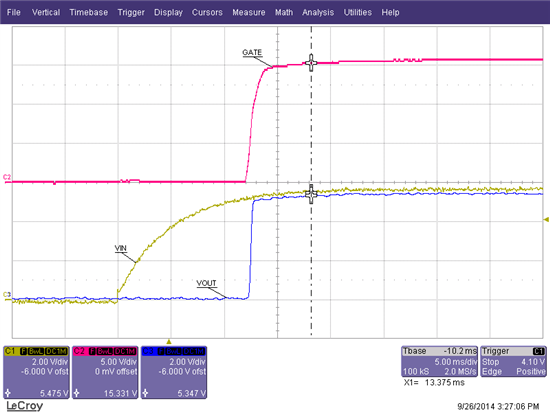

2.Please present the detailed data of the VIN=5V neighborhood about the datasheet 6 page figure3 VGATE vs VIN characteristic.

3.Please give me proposal of the protection circuit which can cope with the protection to negative serge, and power supply reverse connection protection.

The condition of negative serge is followed as:

・Voltage : -600V ・Period : 1msec ・Repetition : 5000times ISO7637-2