Hi,

I have one question about LM25066 as below.

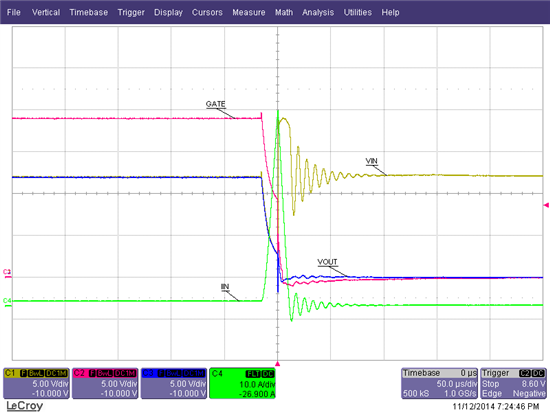

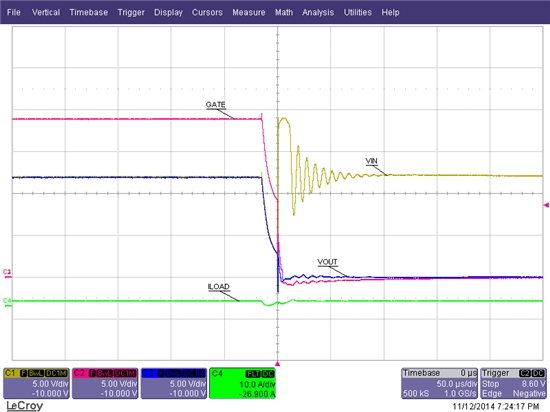

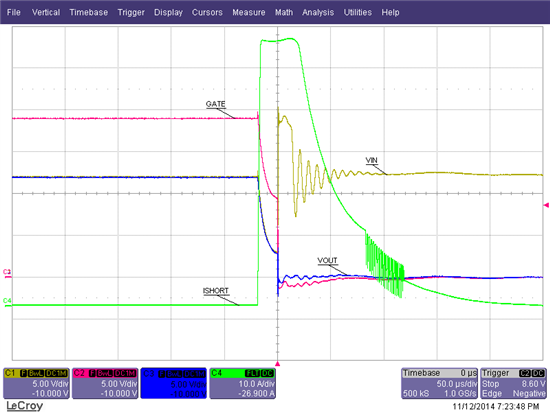

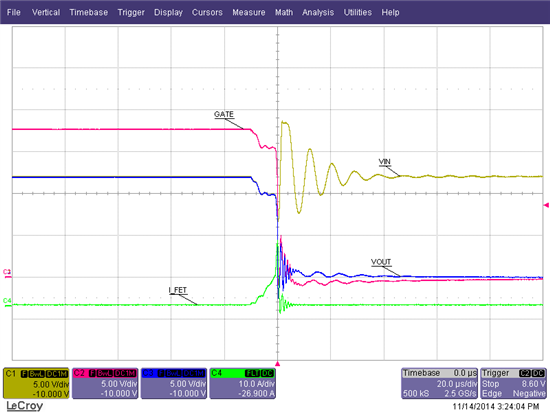

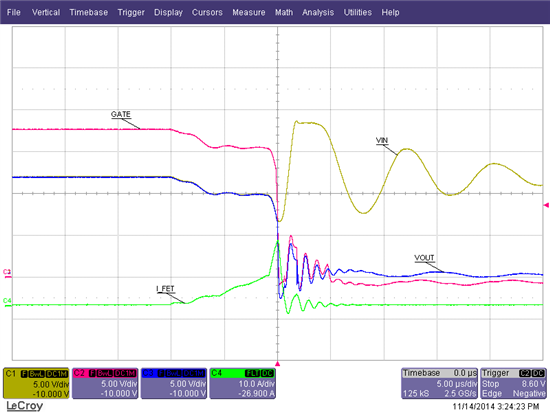

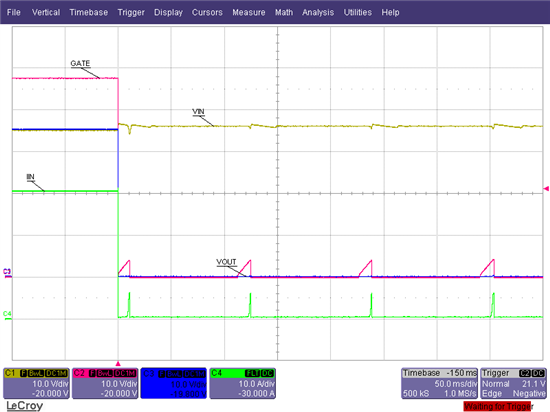

When output is short, is power limit effective here? Please see below waveform of output short test.

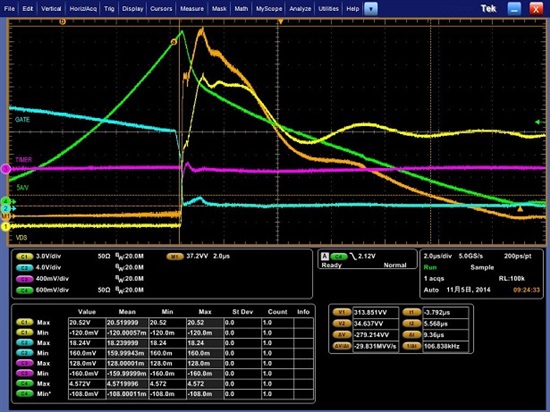

CH1:VIN CH2:VOUT CH3:TIMER CH4: Iout(5A/V) M1: MOS Power (Vds*I)

Power Limit set: 111W

Current Breaker set: ~23A

From waveform, after output is short, maximum MOSFET power is >111W, and maximum current is just ~23A.

Thanks.

Johnny