Other Parts Discussed in Thread: TPS23753

Hi team.

My customer and me has a lot of questions about the MPS of the TPS2373-4.

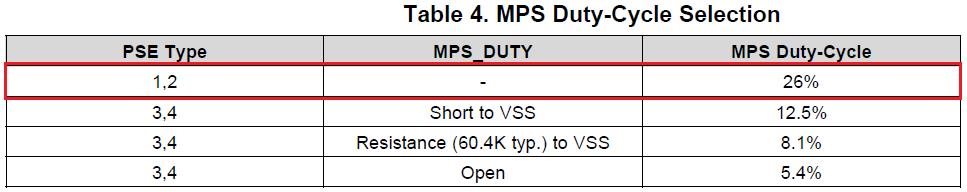

1. Customer's question : How should I configure the circuit of the TPS2373-4 to operate the MPS_Duty of the red box shown in the table below to 26%?

- My question : If I look at the data sheet contents, I know that you will check the type of PSE automatically.

However, there is no detailed description of how the TPS2373 can check the PSE's Type. Please explain.

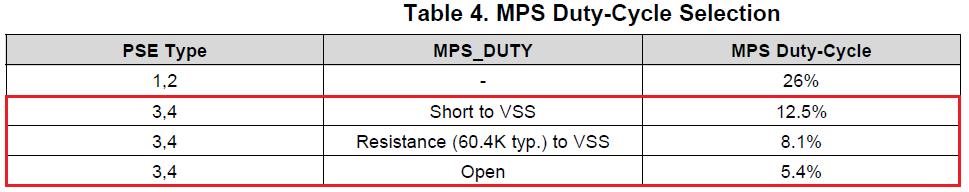

2. Customer's question : Is it appropriate to connect 1.3 ㏀ between the AMPS_CTL pin of the TPS2373-4 and VSS to activate the function of the red box in the table below?

- My question : Looking at the datasheet, RMPS appears to use between 1k and 12k when IRTN is 20mA or less. Is that right?

And I know that RMPS can get the integer through the formula below.

Then, is IMPS value equal to IRTN value? If so, can I calculate the RMPS value by setting the minimum current to the IMPS value when there is no load?

And in the formula for calculating PRMPS, please check why the denominator is multiplied by the duty cycle.

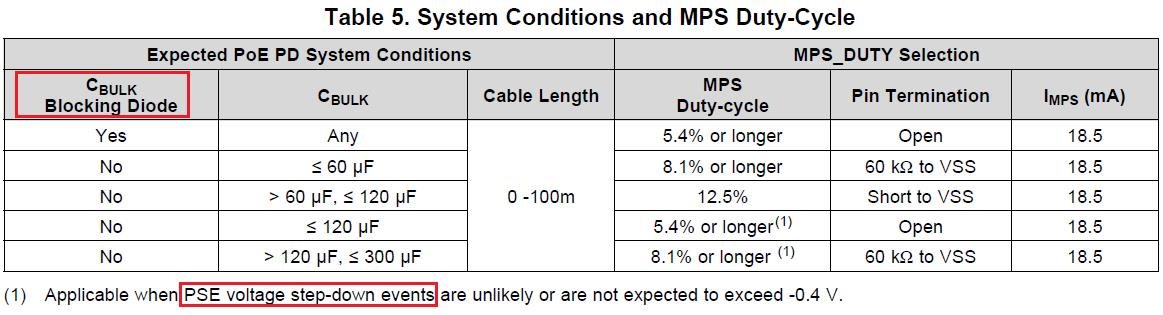

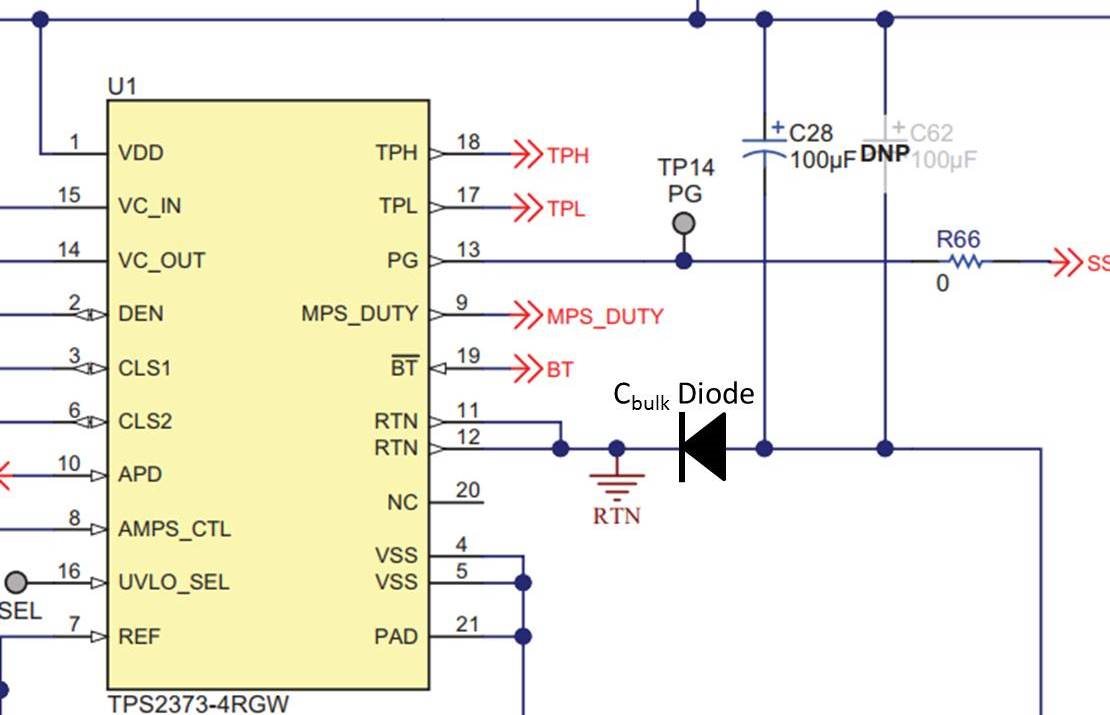

3. Customer's question : What is Cbulk Blocking Diode in a Datasheet or EVM circuit? And Please describe in detail what is the 'PSE voltage step-down events'.

- Refer to the red box in the table below.

4. Customer's question : How to set the Automatic MPS function satisfying PSE Type 1 ~ 4?

Thank you.