Other Parts Discussed in Thread: CSD17510Q5A, CSD18510Q5B, CSD18512Q5B

I made a synchronous rectification circuit by CSD17510Q5A(high side) and CSD17312Q5(low side) with 24Vin.

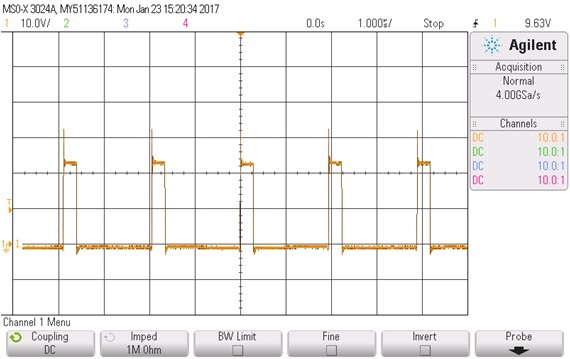

Its switching frequency is 500kHz.

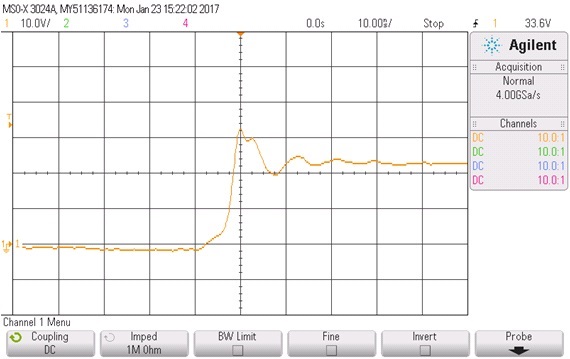

There are measurable ringings at the switching node of my circuit and the peak voltages of them are about 35V.

The duration of the peak over 30V is less than 5ns and its peak is not 'flat-topping'.

I think CSD17312 is not in avalanche mode. Is that right?

Are there any problem about the MOSFET in my circuit?

Best regards