Other Parts Discussed in Thread: CSD18510Q5B

Hello,

I'm making the footprint for this MOSFET to include it in my design, but looking at the PCB Pattern, I get different measurements on it's pad height.

Using the higher tolerance boundaries:

F11=F3=4.56

F3=4*F4+3*F5=4*0.7+3*0.67= 4.81

4.81 is totally different than 4.56

Nevertheless, using the lower tolerance boundaries:

F11=F3=4.46

F3=4*F4+3*F5=4*0.65+3*0.62= 4.46 this measurement matches.

I'm confused, should I calculate the average between these two?

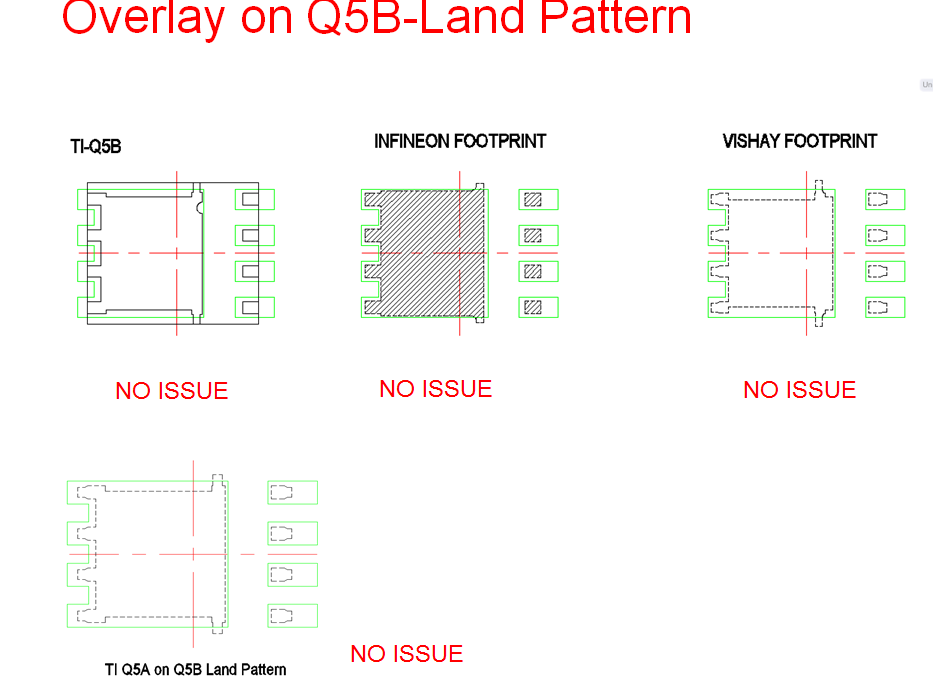

I'm also trying to adapt this footprint so I can use PG-TDSON-8 on the same footprint for alterns like BSC117N08NS5ATMA1

Thanks in advance.