Other Parts Discussed in Thread: LMZ36002, LMZ36002EVM

Hello!

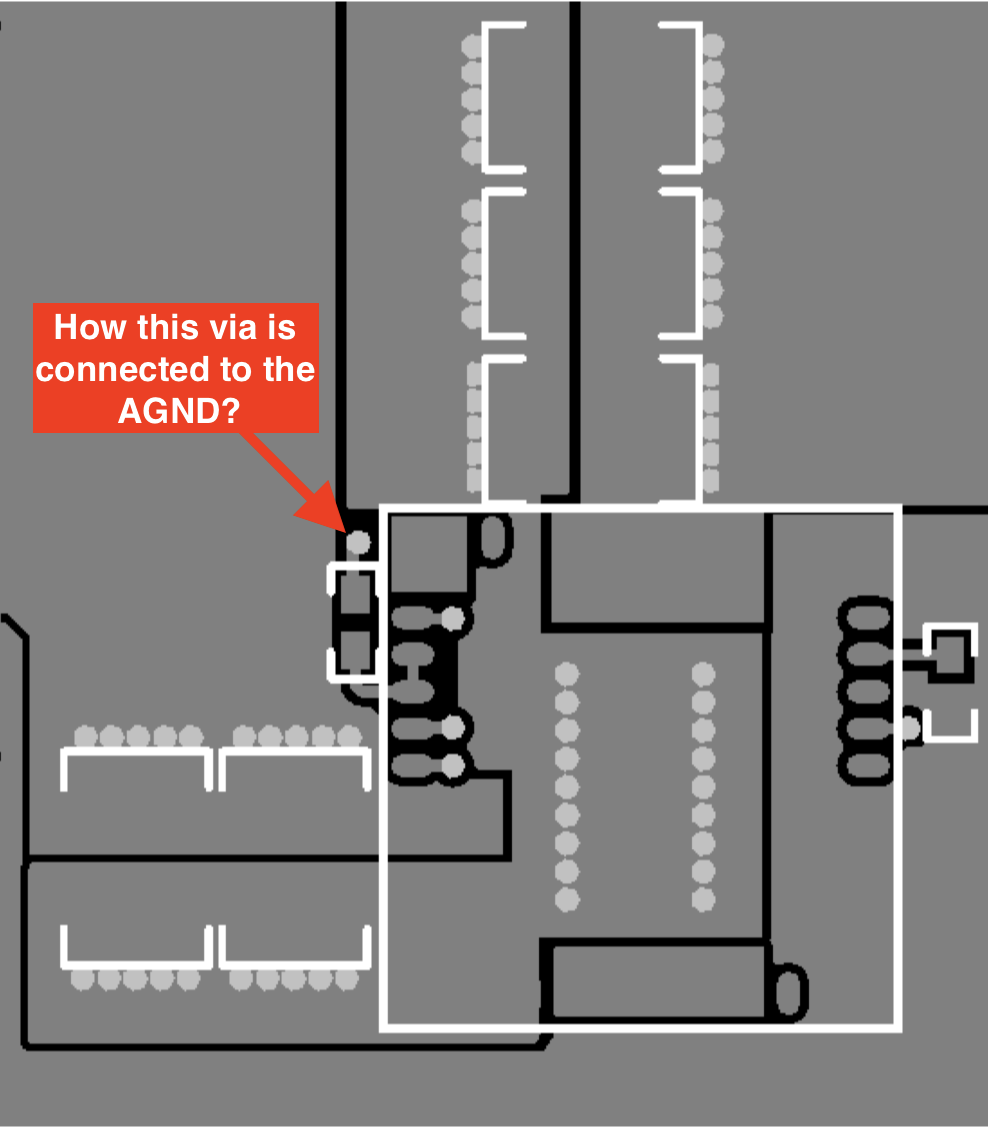

I can't understand Gerbers in TIDA-00783:

1. How R4 is connected to AGND? It's connected to via on top layer, but this via did not connected to anything on other layers.

2. In TIDA-00783: AGND and PGND are connected by via near R3. In LMZ36002 datasheet i see: "Keep AGND and PGND separate from one another. The connection is made internal to the device."

3. In pdf version of layout Mid layers are blank, but in gerbers they are not blank.

4. Can i get layout in Altium or Cadence format?