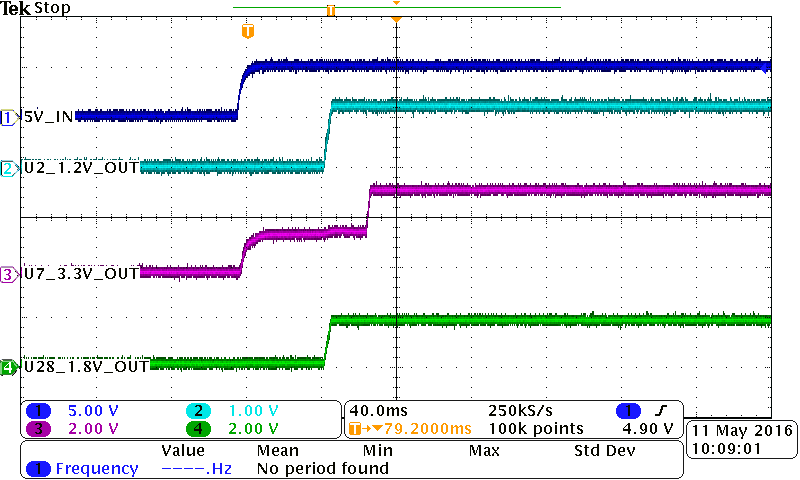

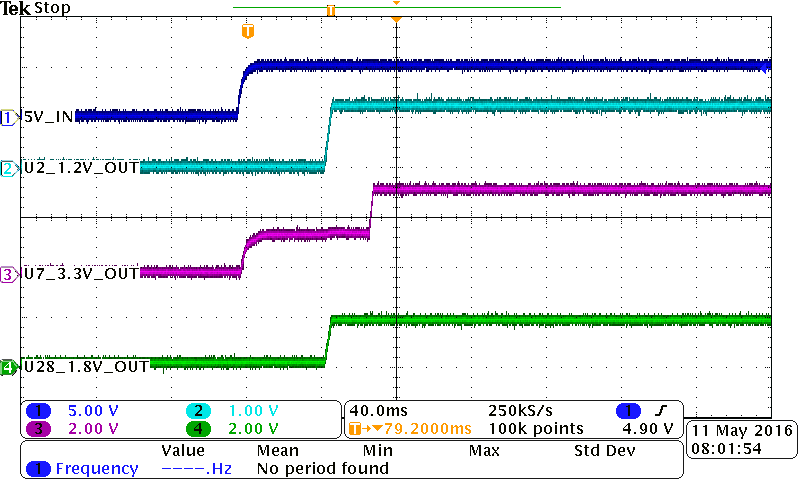

We have had a rash of simple switchers (LMZ10505EXT) failing at cold (-40C). The units work during preliminary test, but fail when the powered on at -40C. When the regulators are removed, the Vout or Vin will measure shorted to ground. We have had about 7 failures since 3/21/2016.

Will Cumby