Hello,

My customer have some questions about TPS386000.

[Their schematic]

Their schematic is as follows.

[Behavior]

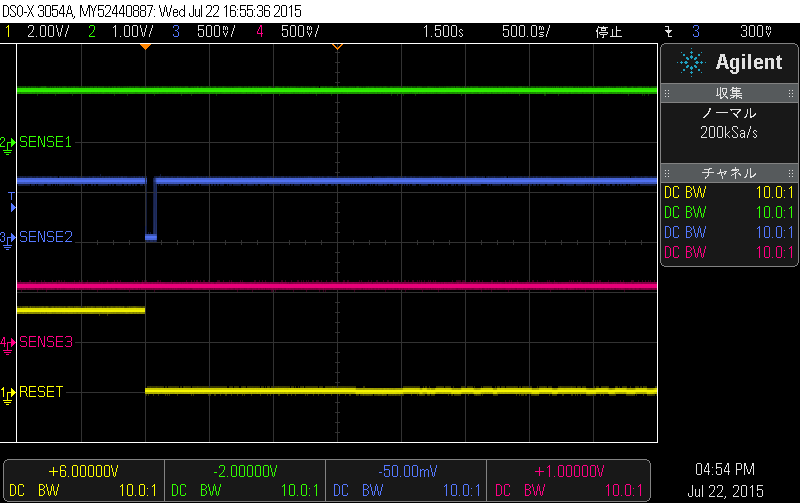

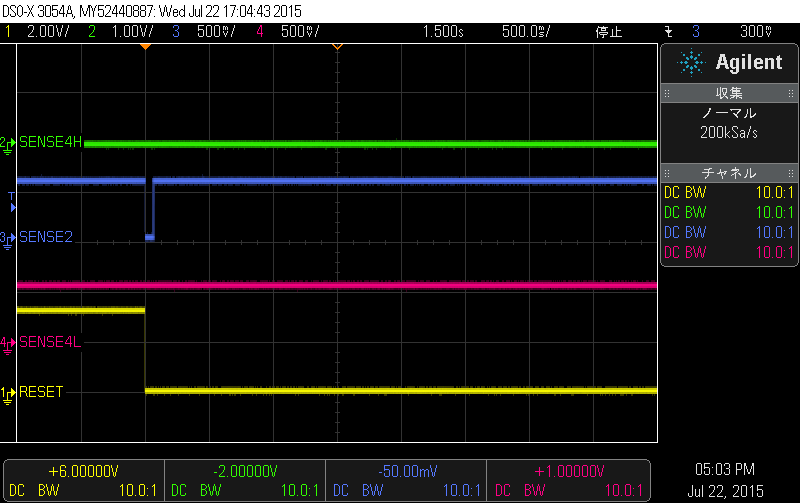

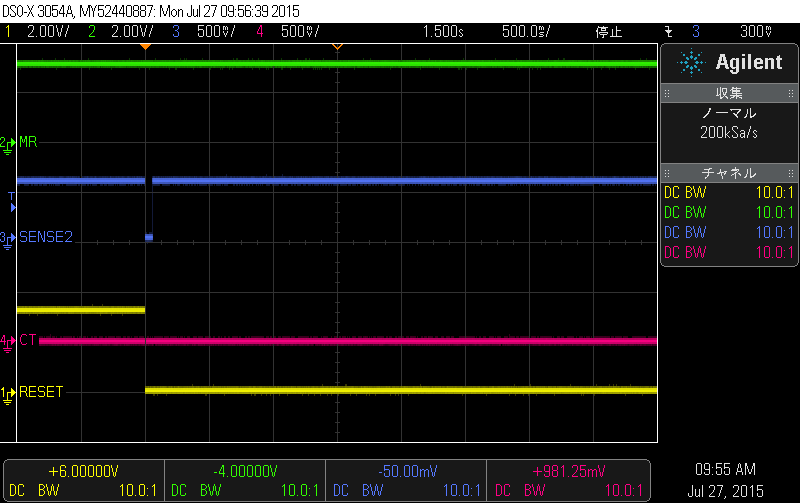

Please see the following.

- SENSE1 & SENSE2 & SENSE3 & SENSE4L > 0.5V > VITN+VHYSN → Reset released after delay → Looks Good.

- After that SENSE2 goes to 0V → Reset asserted → Looks Good.

- After that SENSE2 goes to greater than 0.5V. → Reset still asserted. → Looks Bad. This is irregular behavior.

[Q1]

Is it possible the resistors for CTn are pulled up together?

[Q2]

Do you have any problems for their schematic ?

Please let me know.

Best Regards,

Hiroshi Katsunaga