Hola,

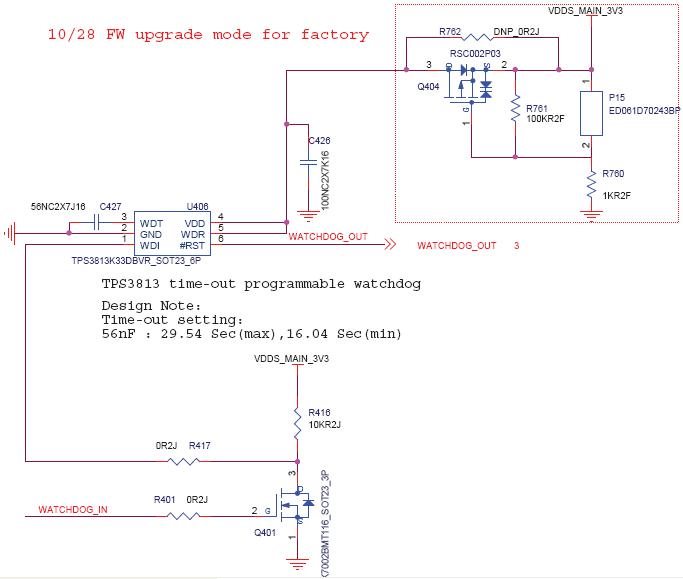

Our customer have a question about the risk of power leak of the TPS3813K33 as below:

The disabling circuit of the watchdog stops to a supply power to watchdog IC(U406). But doesn't it have a risk of error operation?

Because it has a chance of power leak from WDI to RST block. Please confirm this risk to TI.