Dear, All

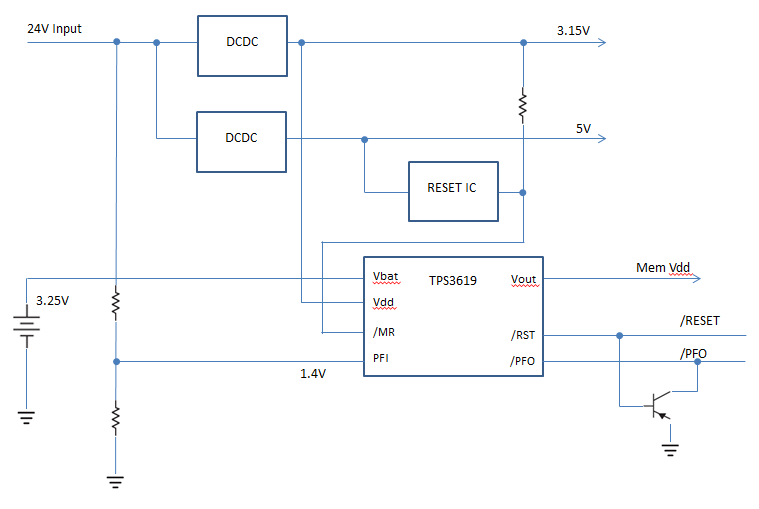

A customer is a circuit using TPS3619, and a problem occurs.

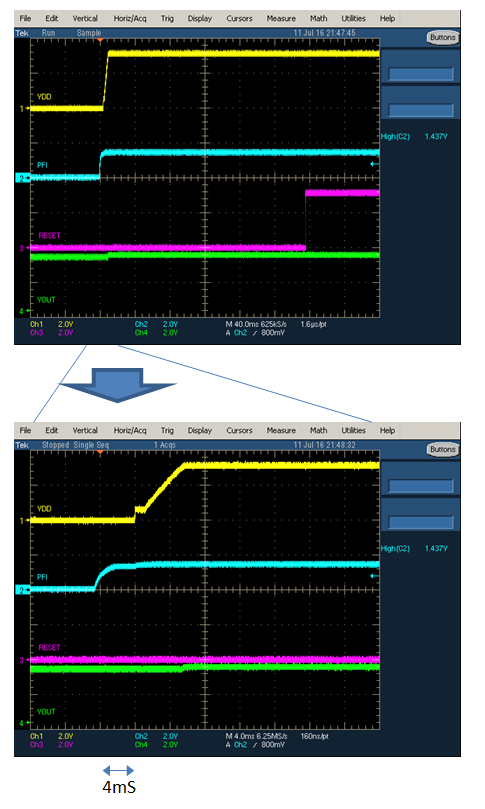

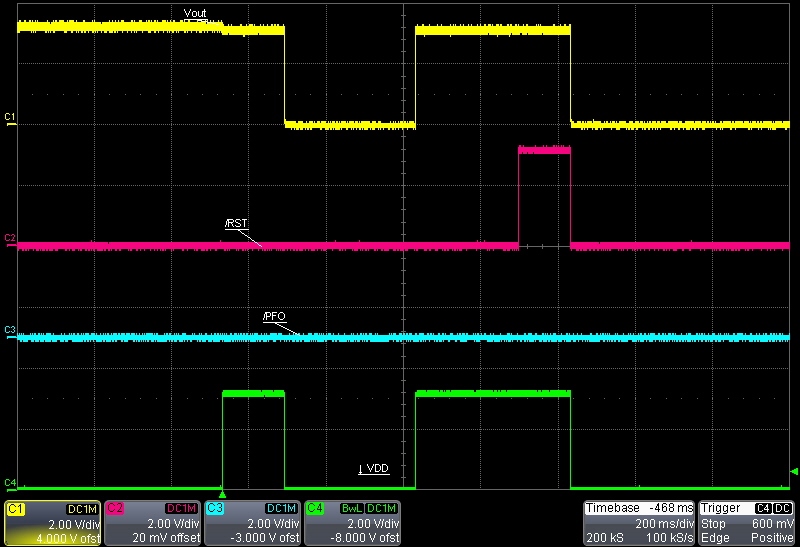

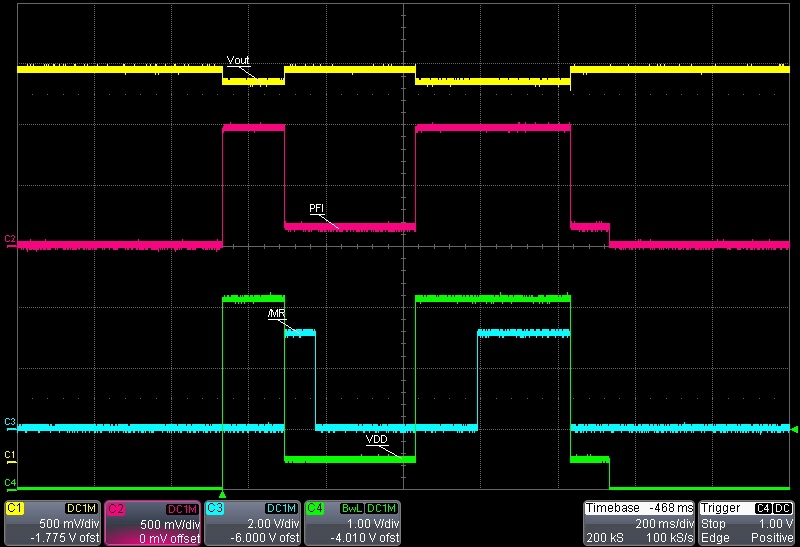

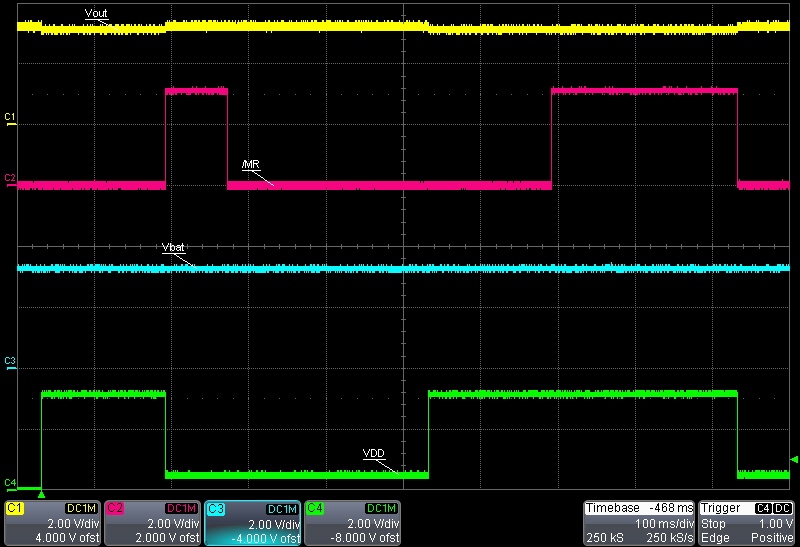

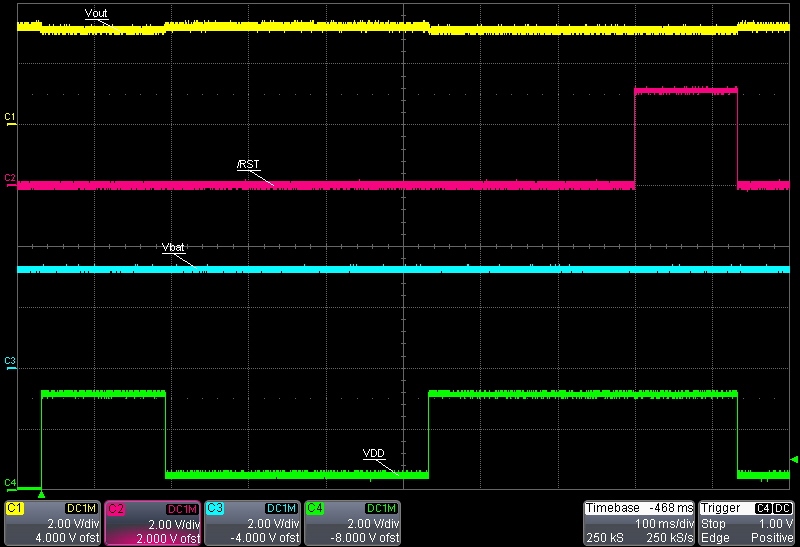

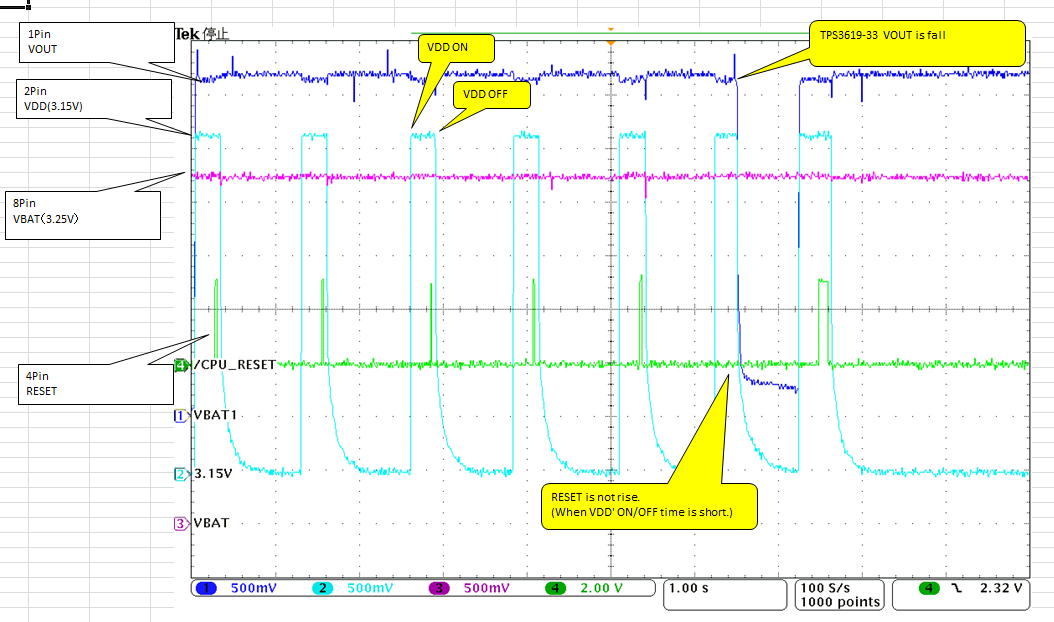

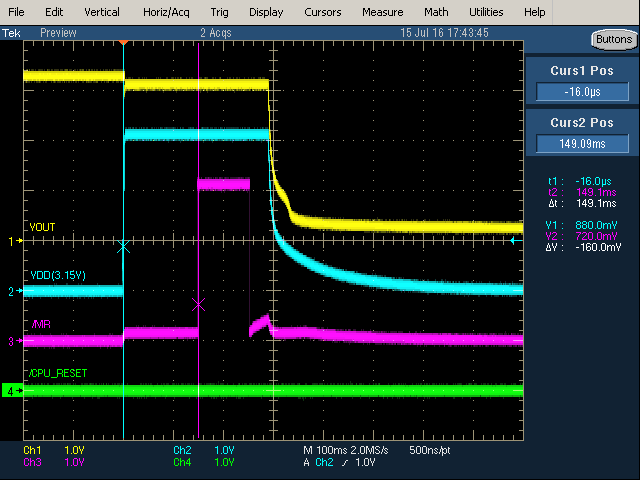

Vout is not output at time when VDD did On/Off in short time.

They suspect that "Battery Freshness Seal" function of TPS3619 worked.

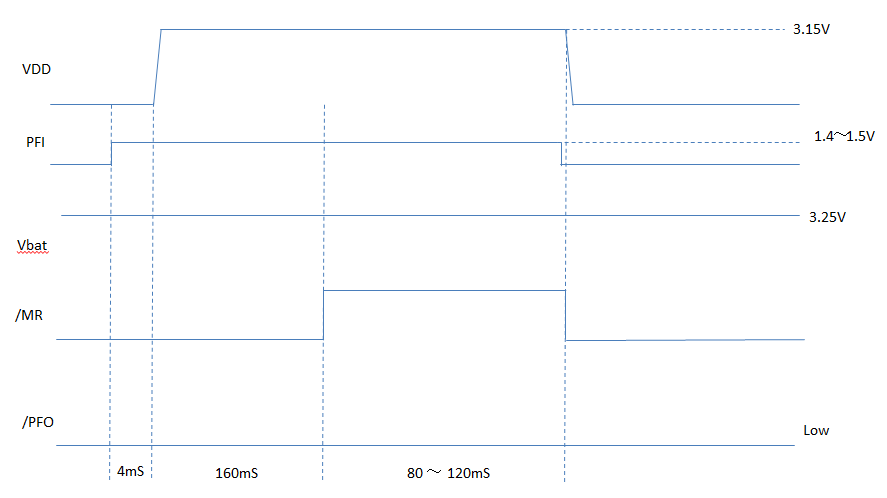

There is a question under conditions of "Battery Freshness Seal" function.

>3. Connect PFI to VDD (PFI = VDD)

They do not connect PFI to VDD.

The input voltage of the PFI is around 1.4V. (VDD=3.15V)

If other conditions match it then, does the "Battery Freshness Seal" function work?

Thanks, Masami M.