Other Parts Discussed in Thread: TMS570LS0232, TPS3890

I require a little clarification of the data sheet for the TPS3852.

When we have a watchdog fault, this will initiate a PORRST event on the TMS570LS0232, since my WDO output is wire-or connected to the output of a 1.25V monitor IC connected to the power-on reset pin of the microcontroller.

Figure 20 of the datasheet shows a typical application where the SET1 input is connected to a TPS3890, which generates a long input pulse to disable the Watchdog timer during reset recovery / power up initialization. This circuit will work well for intial startup, but the concept fails when you have a watchdog induced reset, since you no longer have a disabled watchdog for the second initialization period.

One possible fix for this would be to feed back the watchdog induced reset to the /MR input pin of the TPS3890. This would disable the watchdog by clearing the SET1 input low to repeat the initial power up reset watchdog event.

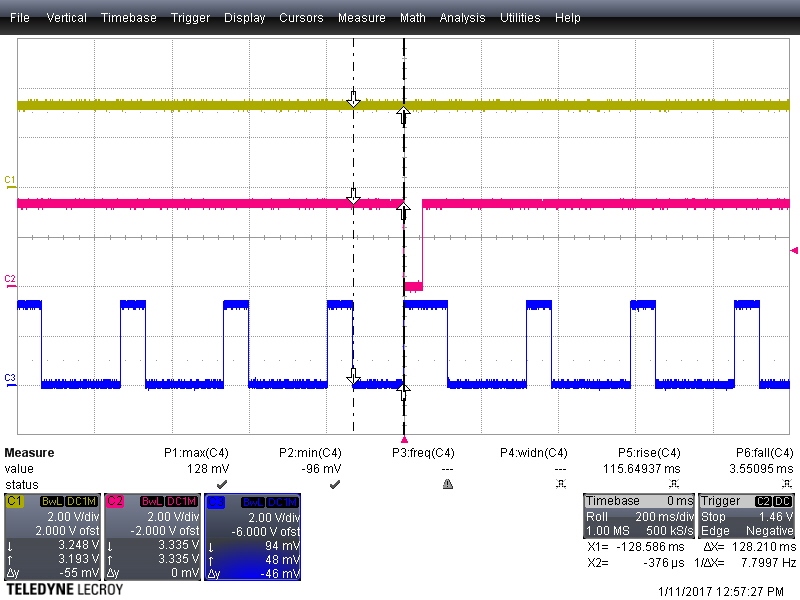

My question is, what happens to the \WDO output if SET1 is cleared low during the 200ms nominal WDO low pulse period? Does the WDO output immediately go high impedance, or does the tRST delay complete before the \WDO pin goes into the high impedance state requested by SET1 low?

Or do I need to use nRST warm reset instead, and initiate watchdog recovery code which immediately services the watchdog once it comes out of reset?