Other Parts Discussed in Thread: LM3880

Does the ESD rating in datasheet section 6.2 apply to all in/out pins of the device or just the sense inputs? Is there any CMOS latchup characterization data available on the MR input and maybe the RESET outputs?

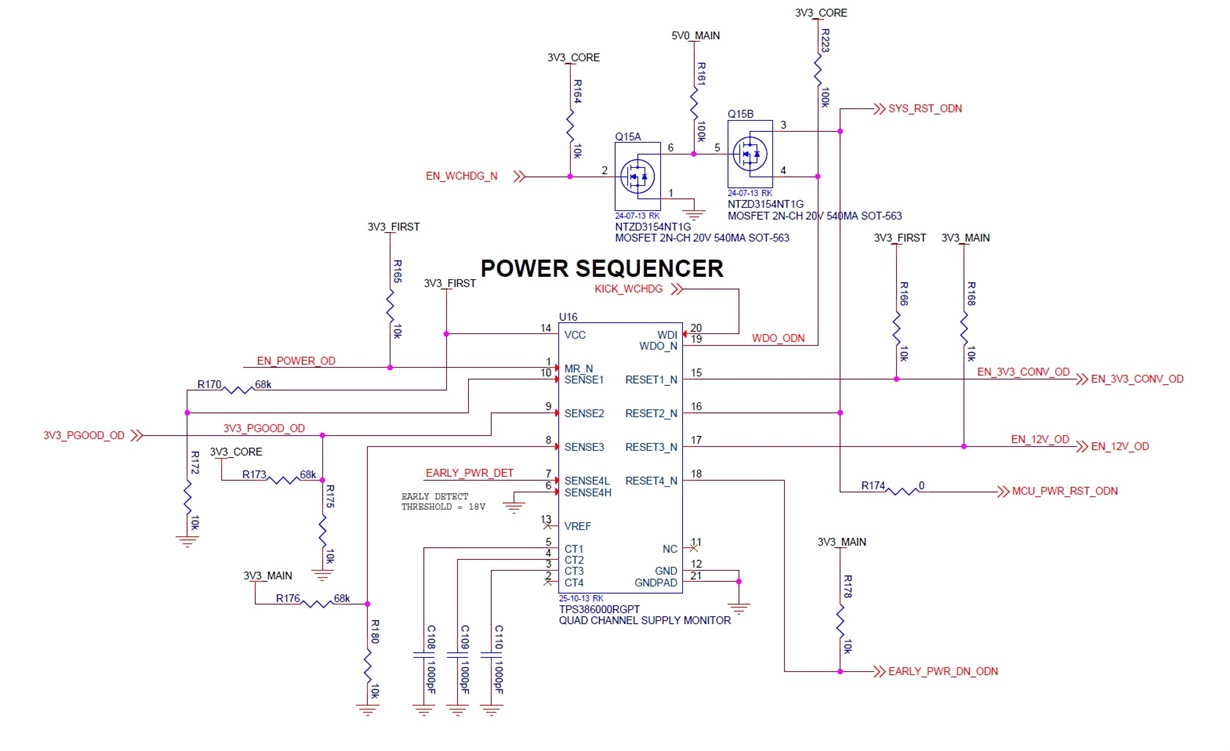

In testing some proto boards that use the TPS386000, some of the power sequence checks involve probing certain nodes of the device to verify timing. It wasn't until about the third board that I noticed the device was not working right with respect to the MR input, and there was also a noticeable jump in idle current on subsequent power-ups following probing.

On the very first 2 boards, after the initial probing, I measured 29-ohms and 145-ohms across the supply rail that feeds the device. Before powering up a third board, I measured around 34K ohms across the rail. With power ON, as I touched scope probes to MR and RESET1, I noticed the current had jumped up from around 1mA at initial power-on to around 82mA. After a power off-on cycle, the higher current persisted, and now the rail measured around 40-ohms. The 3.3V rail of the device is generated by a dedicated linear regulator with clean risetime and no overshoot. The test setup is static protected (grounded benchtop stat-mat, static wriststrap, etc.) and the scope probe GND clips were clamped onto ground plane connected shells on the board.

On the 4th board, I installed diode Vdd/Vss clamping on both pins being probed and was able to continue testing without further incident. Subsequent unmodified boards were powered up and provisioned; those behaved normally and no extra idle current was seen since they were not probed.

It appears the simple act of touching a high-impedance scope probe to those two nodes (not sure which one did the damage) destroyed the chip. I've only ever seen such sensitivity on dedicated crystal osc port pins which typically do not have ESD protection. Subsequent resistance measurements of the two nodes on board 3 showed no less impedance than the 10k pullups being used, to either rail. That suggests the damage is not directly within the input or output structures of the two pins, which could point to an induced latchup event rather than punched gate.