Other Parts Discussed in Thread: TPS3700

I posted it at the end of the following thread, but I also set up another thread just in case.

https://e2e.ti.com/support/power_management/supervisor_reset_ic/f/886/p/667726/2477836#2477836

Will you teach me?

-----------------------------------------------------------------------------------------------------------------------------------------------------------

Thank you for your response.

I am working with "Bob Lee 62837", he is an engineer and I do customer's Q&A support.

I talked with the customer about this matter and the situation was as follows.

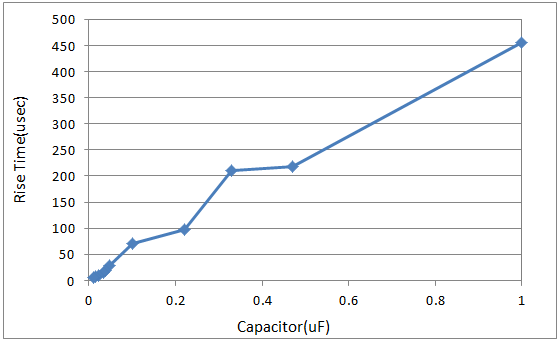

The slew rate of the RESET signal doesn't fluctuate with CT capacity, but in the past there were the following answers.

(We and the customer don’t discuss this answer because we can not confirm who sent this answer in the past.)

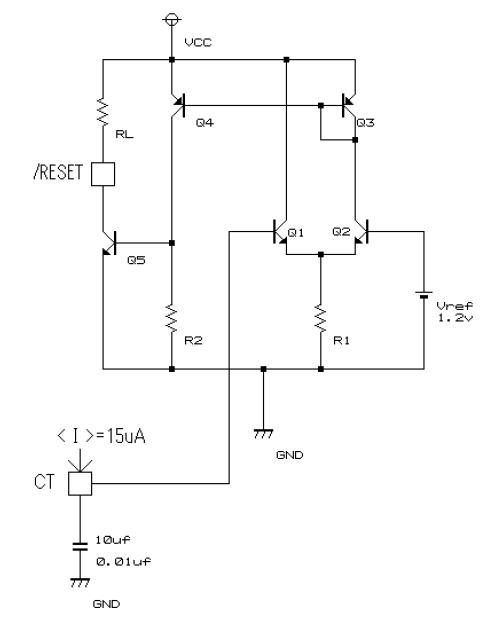

The figure above is a composite of the TL7700's internal and peripheral circuits.

① The comparator output of Q1 and Q2 becomes the current of Q4.

② To make the current of Q4 zero, it is necessary to set the collector current of Q2 to zero.

③ This assumes that the comparators Q1 and Q2 become Q1: ON, Q2: OFF, but a voltage difference of about 50 mV is required for Q1 and Q2.

④ Therefore, if slew rate of CT is loose, it takes time until this voltage difference occurs, during which Q5 also turns ON and the slew rate of RESET signal becomes loose.

Is this consider correct?

if this consider is correct, does the slew rate of RESET signal depends on CT capacity?

Best regards,

Masumi Sekiguchi