Hello,

I have a signal connected to pin 39 (TMS/GPIO22), and the pulse duration is 600 us.

Is there a minimum pulse duration specification for GPIs to ensure the signal is always captured and logged as a fault?

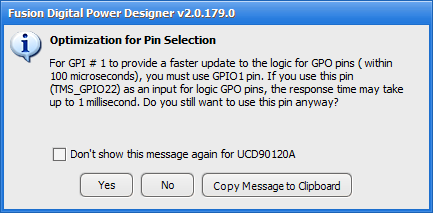

I couldn't find a spec in the datasheet. The below note in the Fusion GUI mentions that there may be a GPO pass-through delay of up to 1 millisecond if using a non-optimized GPI pin mapping, but no mention of the minimum width of the input signal itself.

Thanks,

Jonathan