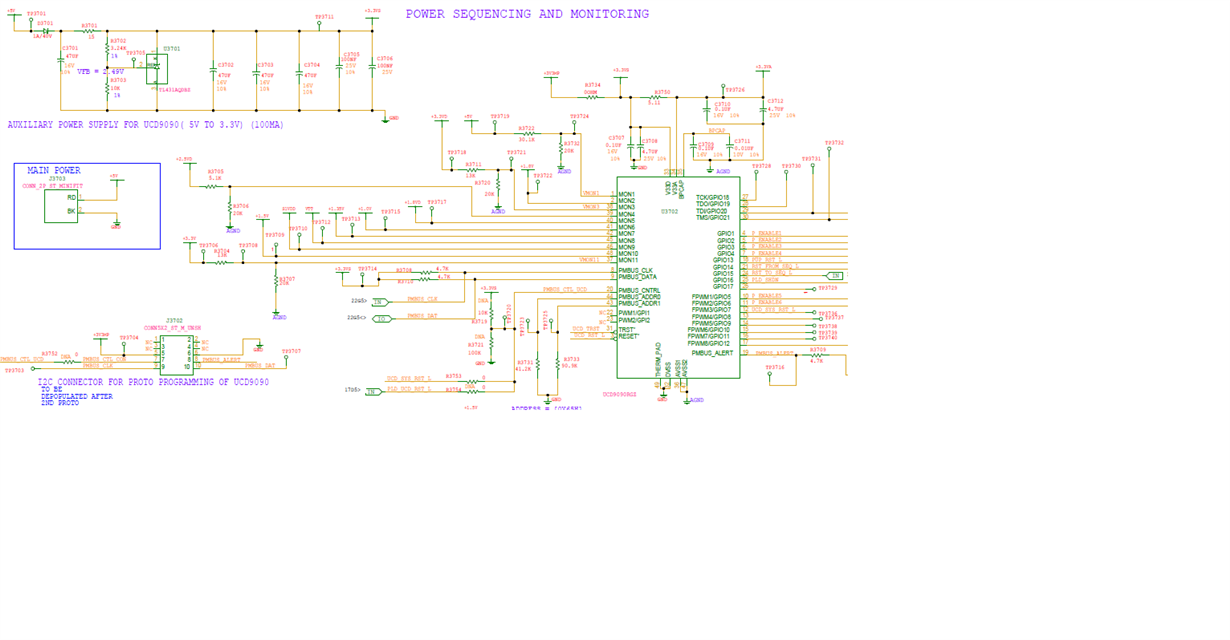

Other Parts Discussed in Thread: TL431,

We are facing few issues on the UCD power cycle functionality.

When we do external power cycle after some 15mins/30mins of continuous board functionality, we are seeing frequent lock on the UCD. UCD is not sending out EN signals for other regulators. Board power rails are not coming out.

We captured the waveforms for external 5V, 3.3VS (UCD supply), board power supplies 3.3V & 1.0V (based on enable signal given from UCD).

Here are the observations from the waveform,

1. When doing fast power cycle when the board is under Longer time of operation:

- 5V rail starts to die down. Immediately it sees an increasing in voltage and later started to fall continuously.

- 3.3VS fall and then retain its stable 3.3VS due to the TL431 device on its path. Then, later 5V to die down.

- If we are not giving longer time for 5V fall and turn on again, some time the UCD is in lock condition and not giving out any output. Looks like the UCD is under lock condition.

- After giving sufficient time from then and then power on we could see UCD functioning.

2. When doing fast power cycle when the board is under Longer time of operation:

- 5V rail starts to die down very sharply and 3.3VS is following it. Even with lesser OFF time duration, when the board gets power, the UCD starts functioning.

- Even we repeated this for multiple times, we could see proper output.

- Only when the off time is very shorter, we are seeing the UCD is not functioning. It gets into a lock condition.

The behavior of power cycle wave for the 5V & 3.3VS is not same between normal operation (lower temp) & at longer operation (higher temp).

One way we are seeing a different behavior on the 5V rail on these two scenarios.

But, very much interested to see, why the UCD is not regaining its functionality even when 3.3VS is stabilized. Would the temperature be a part of this? or Any fault setting could have happen while the 3.3VS is going down to its recommended value and refused to release this even after 3.3VS regains its normal value?

We already removed the 47uf caps on the 5V to 3.3VS conversion circuitry, based on the input we received from previous threads.

We would like to have your support on this.

Regards, UCD9090_FastPowerOn-Off-Test.zip

UCD9090_FastPowerOn-Off-Test.zip

Felix.