Hello,

I'm seeing a strange issue where the enable line for one of my power rails is deasserting for 300-400 µs then reasserting itself. It is the last rail in the sequence. With the logic I have loaded on the power monitor, there are only two ways that should cause the enable line to deassert.

- There is a fault on any of the other rails. This is not happening as far as I can tell. No faults are logged, and the only fault response I have is to shut down immediately without restart.

- The PMBUS_CNTRL line is deasserted. I have probed this line and it does not appear to be deasserting.

My question is thus: Is there any other logic internal to the power monitor that could cause the enable line to deassert without power rail fault or PMBUS_CNTRL going low, or is there a possible bug in the device that could cause such a glitch?

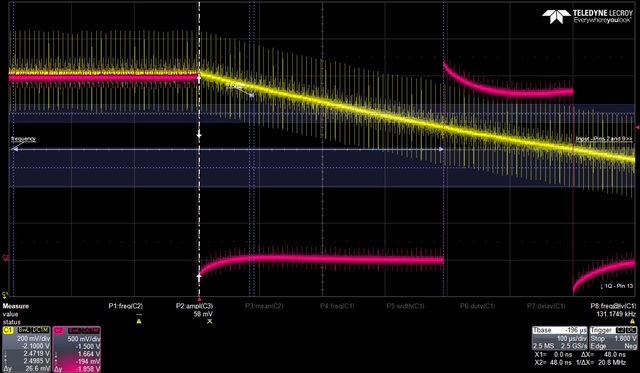

Below is a scope shot of the Enable line in pink and the corresponding rail voltage in yellow. My interpretation is as follows:

- The enable line deasserts for a short period (~400 µs). There was no overvoltage or undervoltage issue and the rail is within the power good thresholds.

- Once the enable line reasserts, the regulator has to go through its softstart process again, so the voltage continues to droop.

- The power monitor sees that the voltage is below the power good threshold (2.25 V) and deasserts the enable line again, causing the rest of the regulators in the system to desequence.

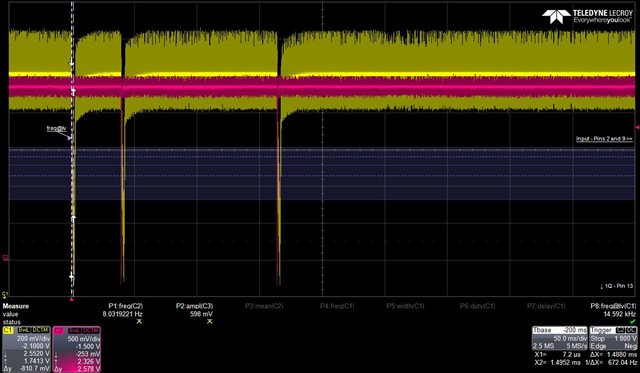

If I lower the POWER_GOOD_OFF threshold to about 1.5 V, the regulator is able to recover, but the enable line continues to drop repeatedly (see image below).

- If the PMBUS_CNTRL line is very briefly deasserted then reasserted, could that cause the behavior described?

- If the nRESET line is very briefly deasserted then reasserted, could that cause the behavior described?

- Once a desequence is initiated, can it be halted and reversed?

Thanks very much for your assistance.

-Stephen Bennett