Got below question:

We use the TI's UCD90124ARGCT sequencer .

I want to have it saving for me the Board HW assembly revision – Can I use it so every power up I know the right HW revision of the board ?

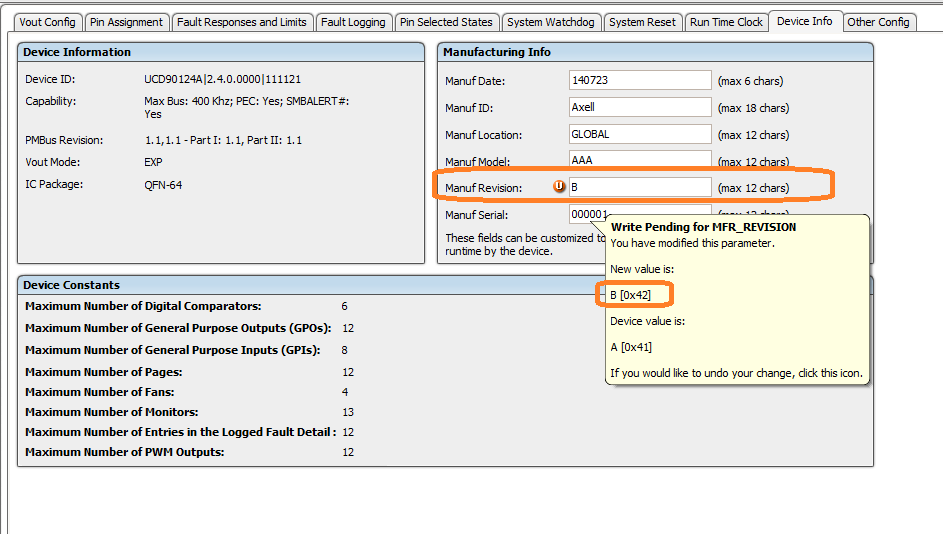

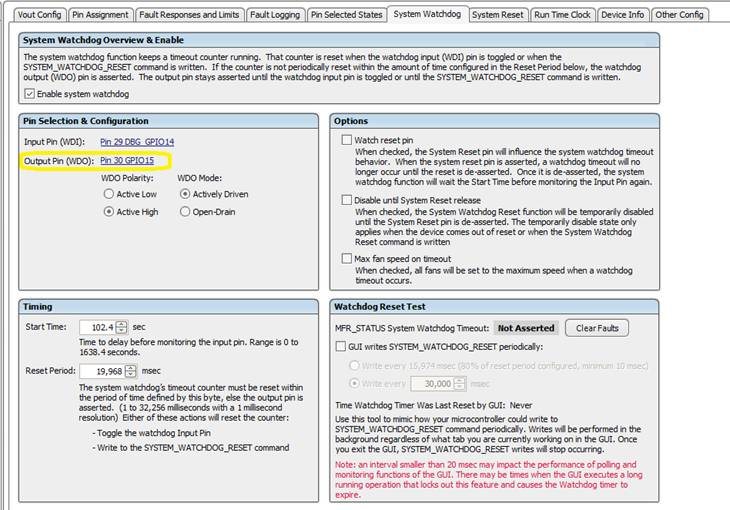

Can it be stored in the marked orange. – Its default is A(0x41) and I am going to change it to B (0x42) as below ?

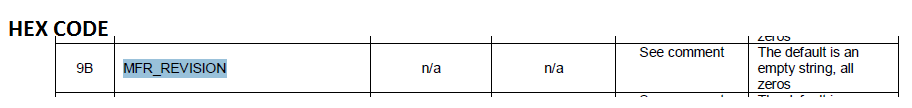

Is the address code is 0x9B ?

Intension is to change in GUI the Board HW assembly revision – then program it into the device flash and after power-up give SW the ability to read it from 0x9B