Other Parts Discussed in Thread: TPS25944A

Hi,

My customer has a question.

This is written in the data sheet.

[The TPS25942, TPS25944 monitor V(IN) and V(OUT) to provide true reverse blocking from output when V(IN) <(V(OUT) – 10 mV).]

But,

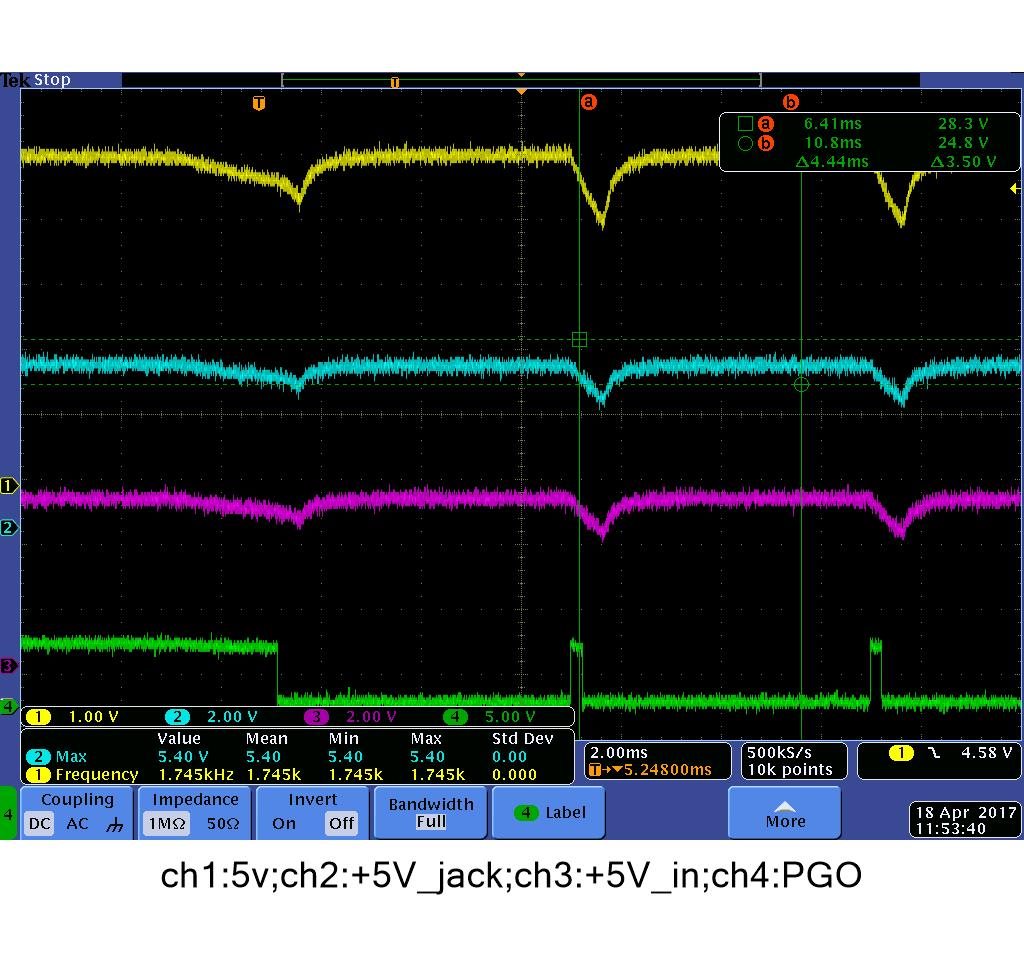

After checking the operation,

Following the rise in VOUT, VIN was also rising.

Is this correct behavior?

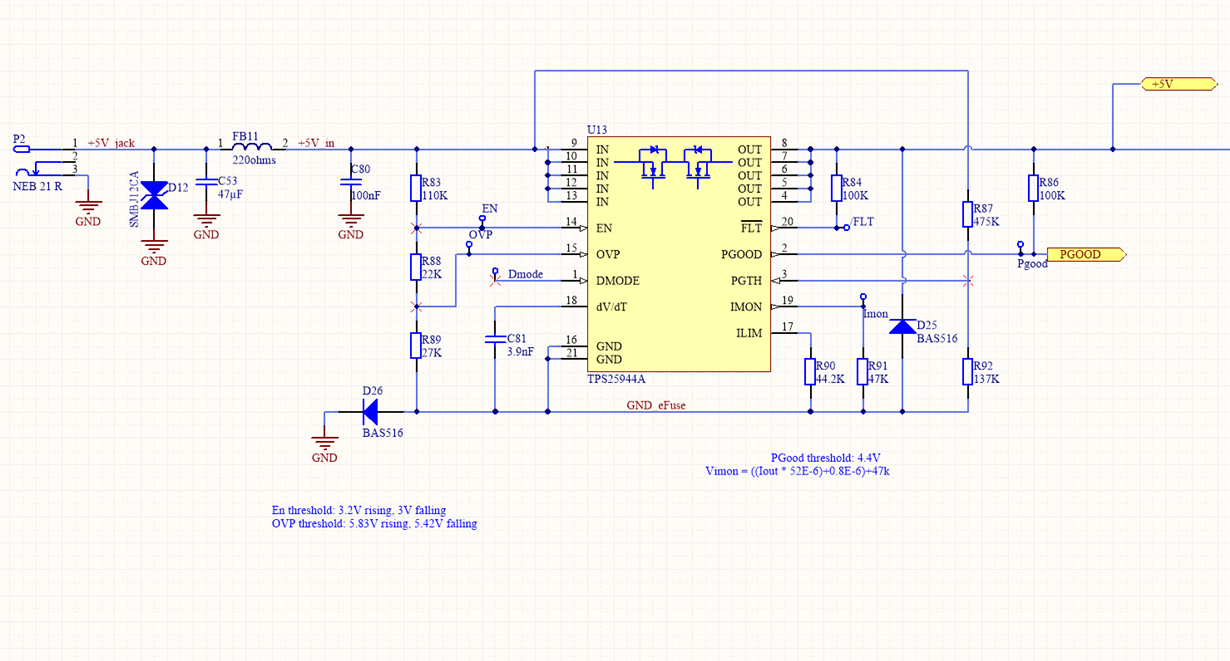

The customer is using the circuit of Figure 87.(Datasheet P44)

Best Regards,

Watanabe