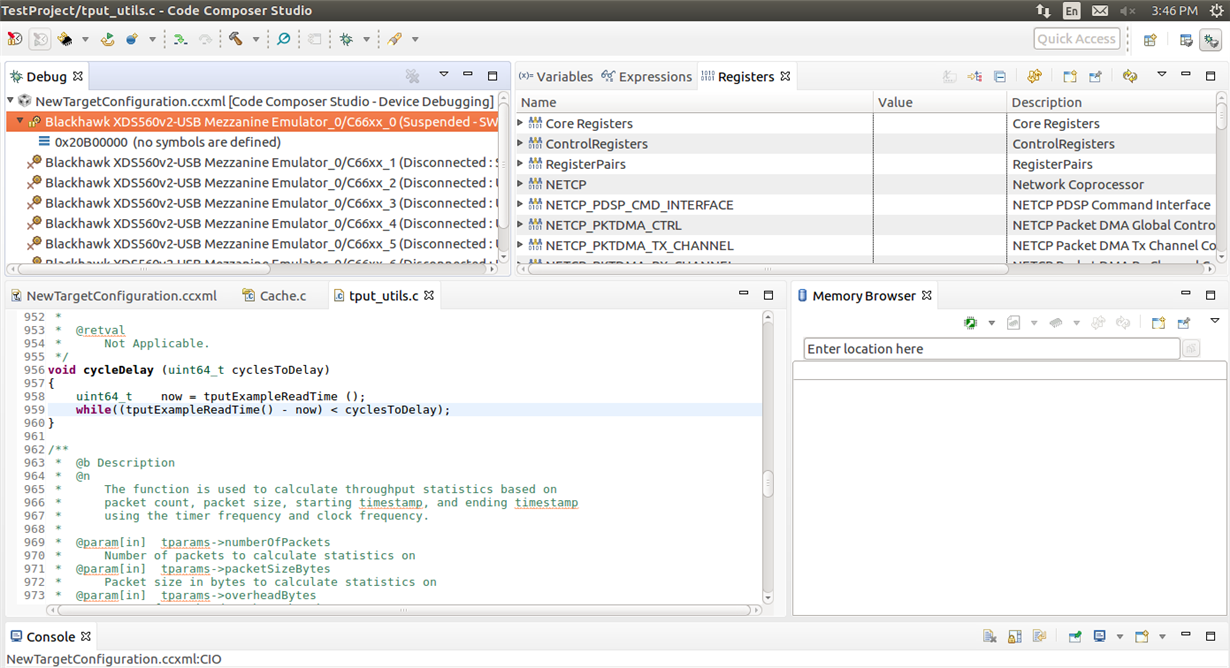

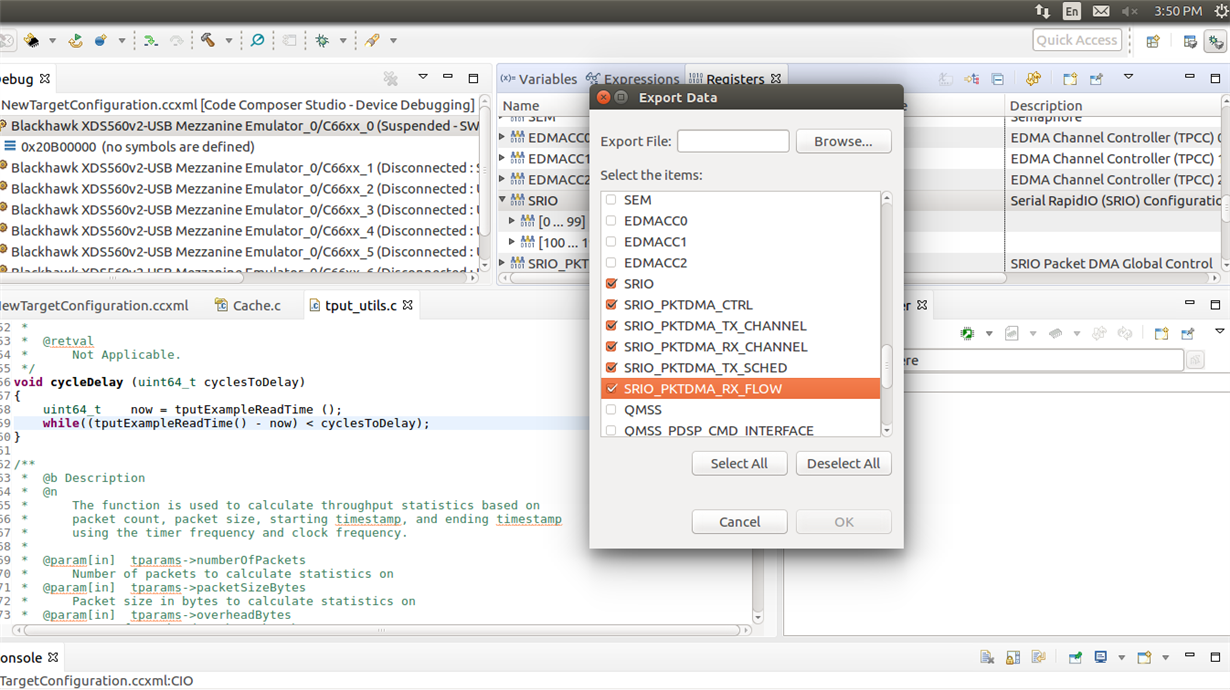

Tool/software: Code Composer Studio

Hi TI experts,

We are configuring a TI DSP (c6657) board to talk to another of c6657 board, and also a Xilinx Zynq board. The set up includes all three boards & a Vadatech UTC 2002 switch in a MicroTCA Chassis. Upon configuring the TI DSP board that we are using as our master for different numbers of lanes (1 or 4 lanes), we do not see a linear change in speeds (very little change in speeds at all, about 10%). We have also noticed that the RIO_PLM_SP_PATH_CTL register shows does show Configuration 4 mode 0 (when attempting single lane) or Configuration 4 mode 4 (while in four lanes). We have compared our results to the "Throughput Performance Guide for KeyStone II Devices" and see that our speed changes should be changing proportionally when changing from 1 lane to 4 lane communications. Ours are most certainly not, but we have done everything in our ability to figure out why, but to no avail.

We also see very different speeds when performing NREADs from TI(A) to TI(B) and from the Zynq to TI(B), which we believe is to be expected because the "TI has eight LSU register sets, allowing for eight outstanding requests for all transaction types that require a response," while the Zynq needs to wait after each packet for the response. Is this what should be expected? We are seeking assistance in finding the root of this issue. Thanks for your time.

Bandwidths:

4 lane NREAD TI(A) to TI(B): 235MB/s

1 lane NREAD TI(A) to TI(B): 226MB/s

4 lane NREAD TI(A) to Zynq: 235MB/s

4 lane NREAD Zynq to TI(B): 19MB/s

1 lane NREAD Zynq to TI(B): 19MB/s