Other Parts Discussed in Thread: TPS65400

Hi K2G team,

My customer is nearing production with their K2G project, and they have an urgent board bring up issue:

"I just received my new board. This board is based on the design of K2G ICE board which has single DDR3L chip. My last board is based on K2G EVM it doesn’t have this issue.

After boot up the board and connected to DSP core(C66x) through JTAG. The reading of BOOTCFG_DEVSTAT Register is 0x005EFEBB which is not the desired values.

The bit of NODDR is 1. This disables EMIF and cannot access DDR3L.

The 4-bit LSB of BOOTMODE should be zeros. We have pulldown resistors, 4.7Kohms for those four pins. They should be 0000b(SLEEP mode for using JTAG) but it shows 1101b.

The LENDIAN is 0. The device endian mode is Big endian instead of desired little endian.

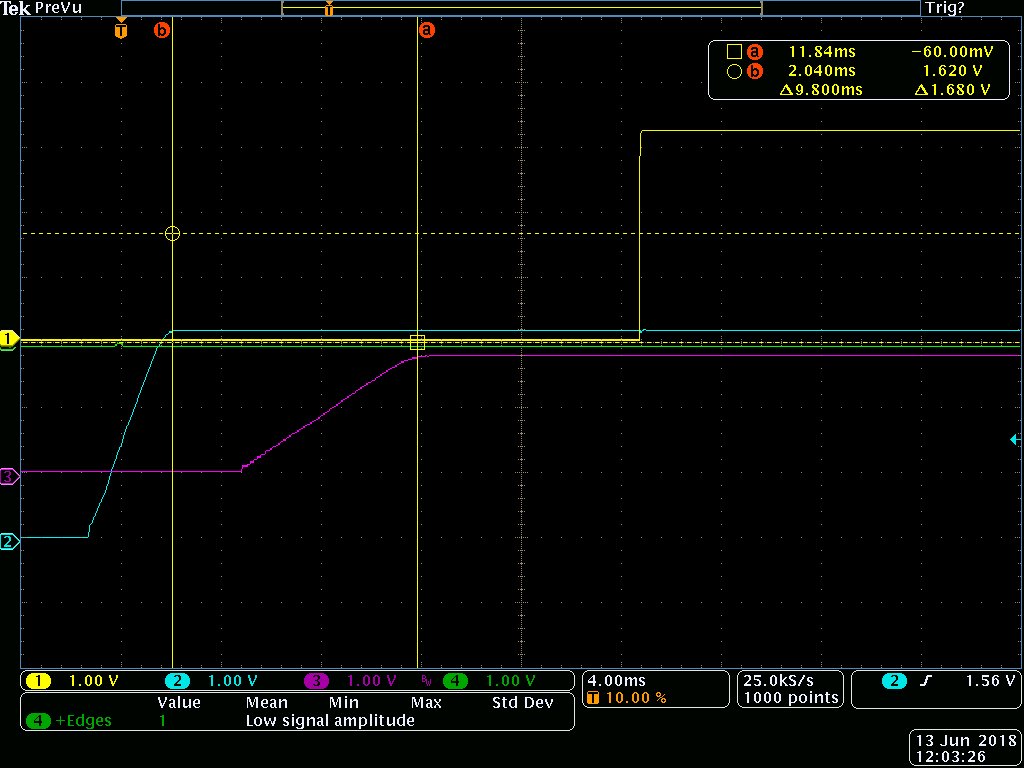

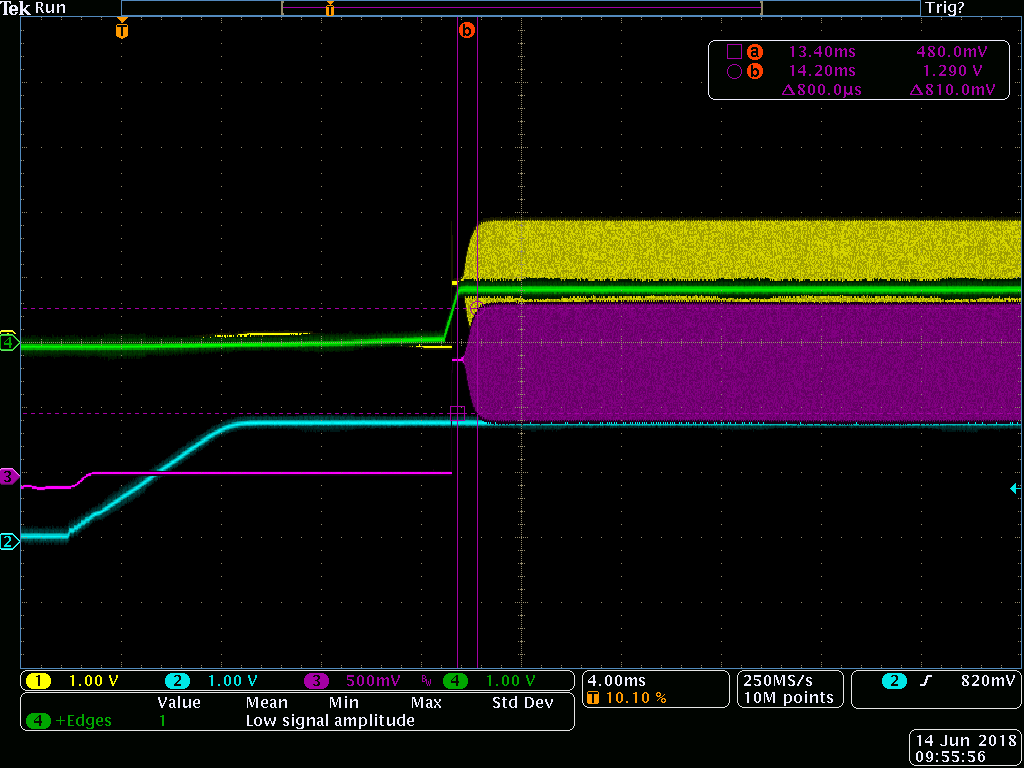

I am going to check PORn and bootmode pins during power up sequence, but can you help point me in the right direction to troubleshoot the undesired value of BOOTCFG_DEVSTAT .

Q1: The bit of NODDR is READ only according to K2G TRM. The pin of NODDR is unconnected in our hardware. Is there any way I can change it to 0?

5.1.4.3 BOOTCFG_DEVSTAT Register (Offset = 20h) [reset = 1h]

BOOTCFG_DEVSTAT is shown in Figure 5-8 and described in Table 5-33.

Indicates device bootstrap selection upon a power-on reset by PORn or RESETFULLn. The default value

of this register is determined by the bootstrap pins. Once set, these bits remain set until a power-on reset.

Q2: Which pin is the LENDIAN bootmode pin? I cannot find it in TRM.

5.1.4.90 BOOTCFG_SYSENDSTAT Register (Offset = 710h) [reset = 0h]

BOOTCFG_SYSENDSTAT is shown in Figure 5-95 and described in Table 5-294.

This register provides a way for reading the system endianness in an endian-neutral way from A15 core.

This register captures the LENDIAN bootmode pin. The value is latched on the rising edge of PORn or

RESETFULLn"

Thanks,

Brian