Hi Team,

I received the following request from a customer I'm following:

################################################################################

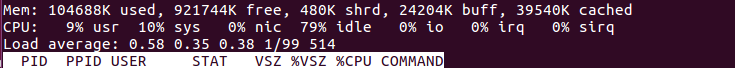

We are currently using the 800MHz version of this CPU in our smart grid node Project.

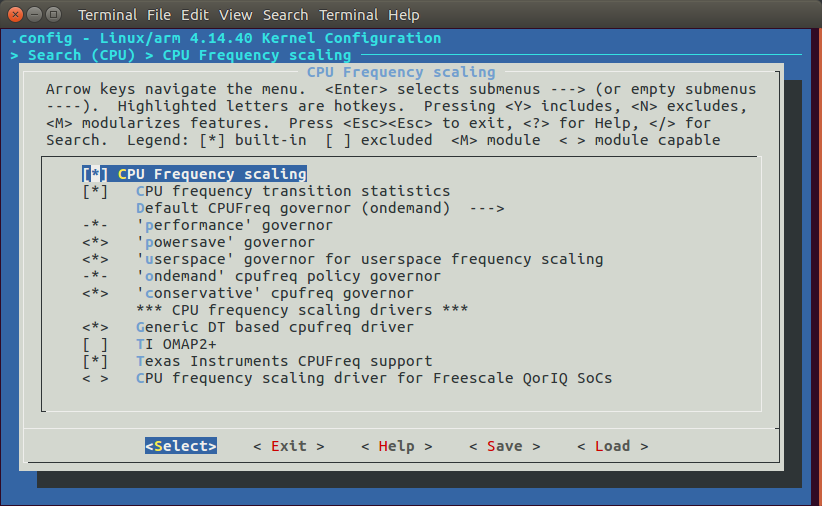

- We are using the Linux distribution published on the TI website (kernel version: 4.14)

- AM4379 is the main processor but we also have other processors in our device.

The other processors communicate with AM4379 over RS-422/UART.

- In our full configuration we use 5 UART each with 1 Mbps speed.

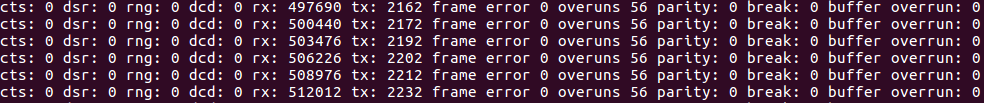

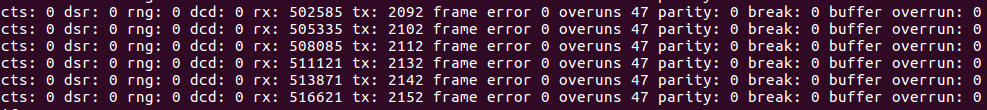

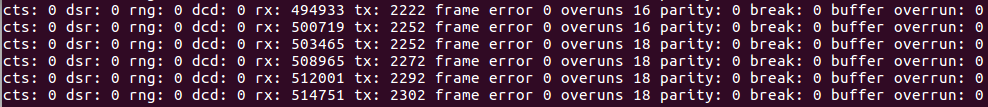

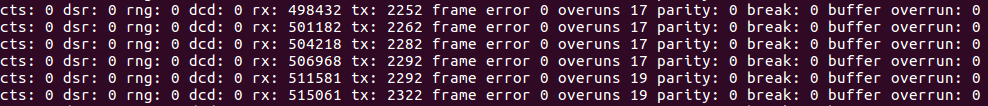

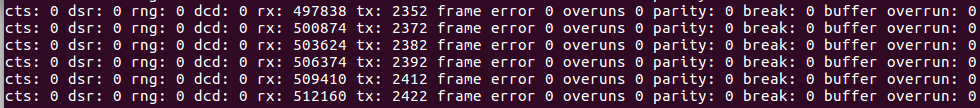

- When we noticed the packet error in our communication, we used serial check and serial stat SW from TI

to diagnose the problem.

- We get Rx buffer overrun error for a certain percentage of the frames received by AM4379.

We observed that some zero bytes are inserted into our data frames in case of error.

- The error rate decreases when we reduce the active UART channels from 5 to 1 but there is still some error.

- The error rate also decreased when we reduced the speed from 1Mbit to 500 Kbps but there is still some error.

And this is not a good solution because we need fast data transfer for some device features. We hope we will be able

to use the UART even with higher baud rates (at least 2-3 Mbps) in some coming projects.

- Currently we handled the packet error with a data link protocol but I hope you can propose a better

solution to this issue.