Hello,

Analyzing the boot procedure of a TI AM5K2E04 we tumbled over an unexpectedly long period of time between the end of the reset sequence and the entrance of U-Boot.

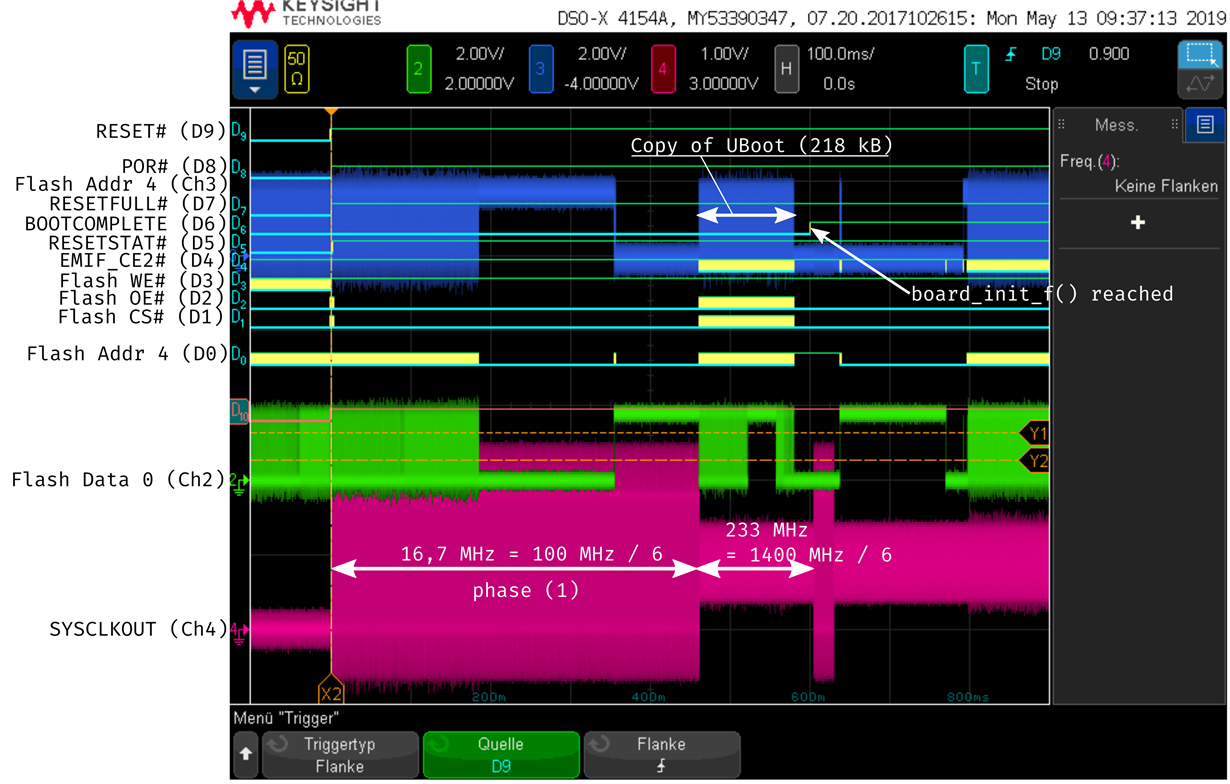

BOOTCOMPLETE pin is used to indicate the beginning of U-Boot function board_init_f(), where we set the BOOTCOMPLETE register at address 0x0262013C to 0xFFFFFFFF to generate a rising edge of BOOTCOMPLETE pin (pin AF31).

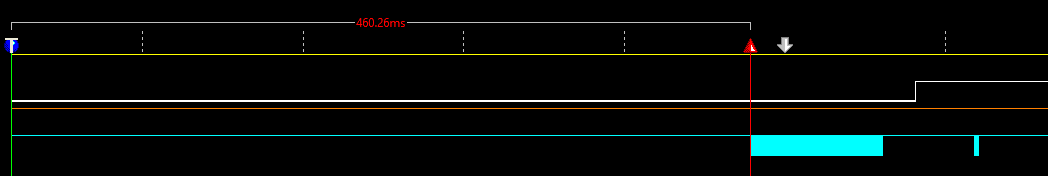

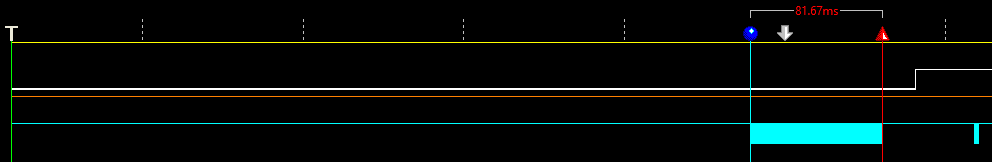

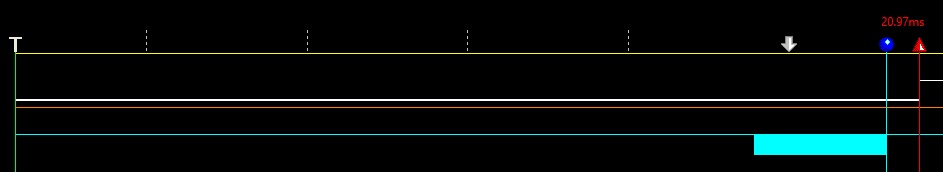

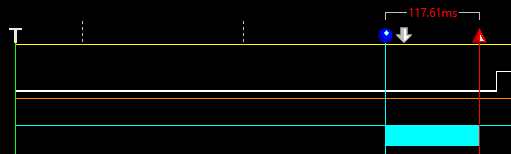

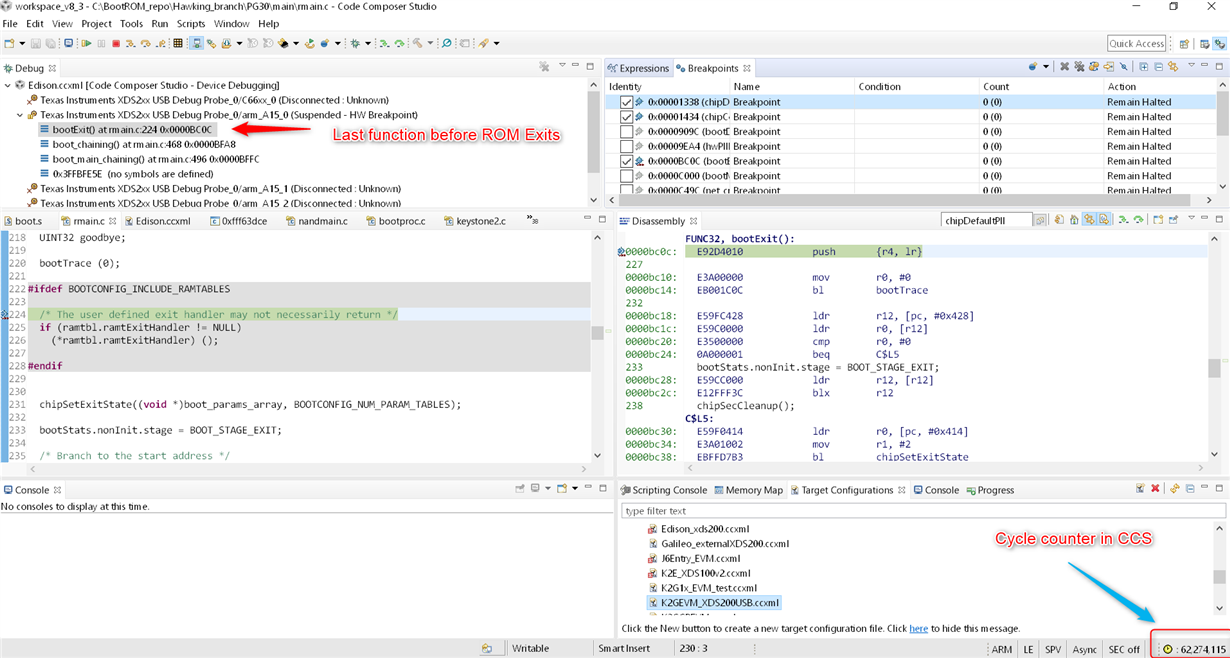

Between the end of the reset (rising edge of RESETSTAT#, pin AH29) and the entrance of board_init_f() a duration as long as 560 ms elapses (measured with oscilloscope). We can't explain this timespan to ourselves, as we for example expect a duration of about 60 ms to copy the U-Boot (about 150 kB in size); we are using EMIF Boot mode.

Is it plausible that almost 600 ms elapse from the end of reset to the entrance of board_init_f()? What’s going on during this time?

Thanks, best regards

Lennart