Other Parts Discussed in Thread: AM5728

Hi ,

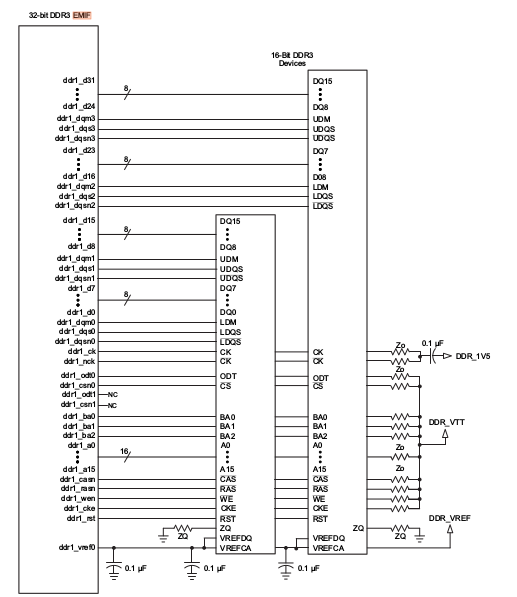

We developed AM5718 based SOM, and we using IS43TR16256A-125KBL-TR 2X RAM chip

I configured DDR3 memory using this EMIF tool in that spread sheet unable to change "Detail 1" value after filling remaining cell I am getting the following output.

/* =========================================================================

* Copyright (C) 2017 Texas Instruments Incorporated

*

* All rights reserved. Property of Texas Instruments Incorporated.

* Restricted rights to use, duplicate or disclose this code are

* granted through contract.

*

* The program may not be used without the written permission

* of Texas Instruments Incorporated or against the terms and conditions

* stipulated in the agreement under which this program has been

* supplied.

* ========================================================================= */

/*

* AM571x_DDR3L_666MHz_TI_AM574x_EVM_config.c

* Created on: 05/03/2019

* Created with: EMIF_RegisterConfig_v2.0.2

*/

#include "emif4d5_wrapper.h"

const struct dpll_params AM571x_DDR3L_666MHz_TI_AM574x_EVM_pll_params = {

.m = 333,

.n = 4,

.m2 = 2,

.m4_h11 = 8

};

const struct ctrl_ioregs AM571x_DDR3L_666MHz_TI_AM574x_EVM_ctrl_ioregs = {

.ctrl_ddr3ch = 0x60606060,

.ctrl_ddrch = 0x40404040,

.ctrl_ddrio_0 = 0x00094A40,

.ctrl_ddrio_1 = 0x00000000,

.ctrl_emif_sdram_config_ext = 0x0000C123

};

const struct dmm_lisa_map_regs AM571x_DDR3L_666MHz_TI_AM574x_EVM_dmm_regs = {

.dmm_lisa_map_0 = 0x00000000,

.dmm_lisa_map_1 = 0x00000000,

.dmm_lisa_map_2 = 0x80700100,

.dmm_lisa_map_3 = 0xFF020100,

.is_ma_present = 0x1

};

const struct emif_regs AM571x_DDR3L_666MHz_TI_AM574x_EVM_emif_regs = {

.sdram_config_init = 0x61862BB2,

.sdram_config = 0x61862BB2,

.sdram_config2 = 0x00000000,

.ref_ctrl = 0x0000514D,

.ref_ctrl_final = 0x0000144A,

.sdram_tim1 = 0xD3337834,

.sdram_tim2 = 0x30B37FE3,

.sdram_tim3 = 0x407F8AD8,

.read_idle_ctrl = 0x00050000,

.zq_config = 0x5007190B,

.temp_alert_config = 0x00000000,

.emif_rd_wr_lvl_rmp_ctl = 0x80000000,

.emif_rd_wr_lvl_ctl = 0x00000000,

.emif_ddr_phy_ctlr_1_init = 0x0824400E,

.emif_ddr_phy_ctlr_1 = 0x0E24400E,

.emif_rd_wr_exec_thresh = 0x00000305,

.emif_ecc_ctrl_reg = 0x00000000,

.emif_ecc_address_range_1 = 0x3FFF0000,

.emif_ecc_address_range_2 = 0x00000000,

};

/*

* DLL Ratio Values are an estimate based on trace lengths. Either

* software leveling or hardware leveling should be performed to

* determine final DLL values.

*/

const unsigned int AM571x_DDR3L_666MHz_TI_AM574x_EVM_emif1_ext_phy_regs [] = {

, // EMIF1_EXT_PHY_CTRL_1

, // EMIF1_EXT_PHY_CTRL_2

, // EMIF1_EXT_PHY_CTRL_3

, // EMIF1_EXT_PHY_CTRL_4

, // EMIF1_EXT_PHY_CTRL_5

, // EMIF1_EXT_PHY_CTRL_6

, // EMIF1_EXT_PHY_CTRL_7

, // EMIF1_EXT_PHY_CTRL_8

, // EMIF1_EXT_PHY_CTRL_9

, // EMIF1_EXT_PHY_CTRL_10

, // EMIF1_EXT_PHY_CTRL_11

, // EMIF1_EXT_PHY_CTRL_12

, // EMIF1_EXT_PHY_CTRL_13

, // EMIF1_EXT_PHY_CTRL_14

, // EMIF1_EXT_PHY_CTRL_15

, // EMIF1_EXT_PHY_CTRL_16

, // EMIF1_EXT_PHY_CTRL_17

, // EMIF1_EXT_PHY_CTRL_18

, // EMIF1_EXT_PHY_CTRL_19

, // EMIF1_EXT_PHY_CTRL_20

, // EMIF1_EXT_PHY_CTRL_21

, // EMIF1_EXT_PHY_CTRL_22

, // EMIF1_EXT_PHY_CTRL_23

, // EMIF1_EXT_PHY_CTRL_24

, // EMIF1_EXT_PHY_CTRL_25

, // EMIF1_EXT_PHY_CTRL_26

, // EMIF1_EXT_PHY_CTRL_27

, // EMIF1_EXT_PHY_CTRL_28

, // EMIF1_EXT_PHY_CTRL_29

, // EMIF1_EXT_PHY_CTRL_30

, // EMIF1_EXT_PHY_CTRL_31

, // EMIF1_EXT_PHY_CTRL_32

, // EMIF1_EXT_PHY_CTRL_33

, // EMIF1_EXT_PHY_CTRL_34

, // EMIF1_EXT_PHY_CTRL_35

// EMIF1_EXT_PHY_CTRL_36

};

struct emif_cfg AM571x_DDR3L_666MHz_TI_AM574x_EVM = {

.platform = "AM571x_DDR3L_666MHz_TI_AM574x_EVM",

.EMIF2_DEFINED = 0,

.pll_regs = &AM571x_DDR3L_666MHz_TI_AM574x_EVM_pll_params,

.ctrl_regs = &AM571x_DDR3L_666MHz_TI_AM574x_EVM_ctrl_ioregs,

.dmm_regs = &AM571x_DDR3L_666MHz_TI_AM574x_EVM_dmm_regs,

.regs = &AM571x_DDR3L_666MHz_TI_AM574x_EVM_emif_regs,

.phy_regs1 = AM571x_DDR3L_666MHz_TI_AM574x_EVM_emif1_ext_phy_regs,

};

Question is where can i apply all this values in source code?

Regards,

Ravi