Tool/software: Code Composer Studio

Hi.

I use evm6678, MCSDK 2.1.2.6 and CCS 8.3.

I am going to use the HyperLink function in addition to the customer's request.

The customer's board has two 6678 DSPs designed.

So I'm trying to test the example project from EVM6678 to LOOPBACK mode, but I don't understand, so I ask.

(hyplnk_exampleProject)

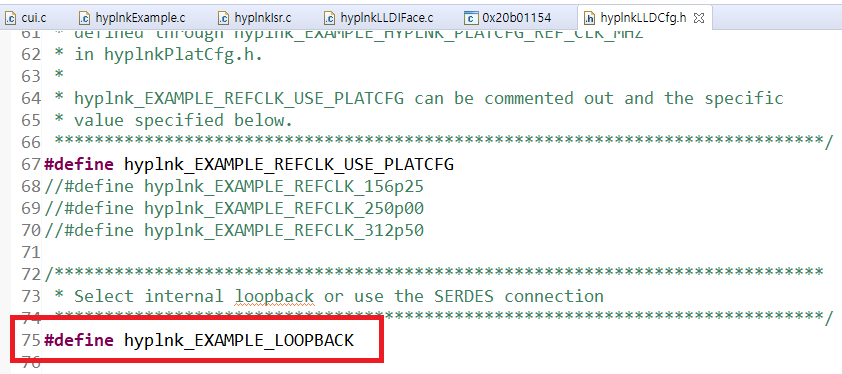

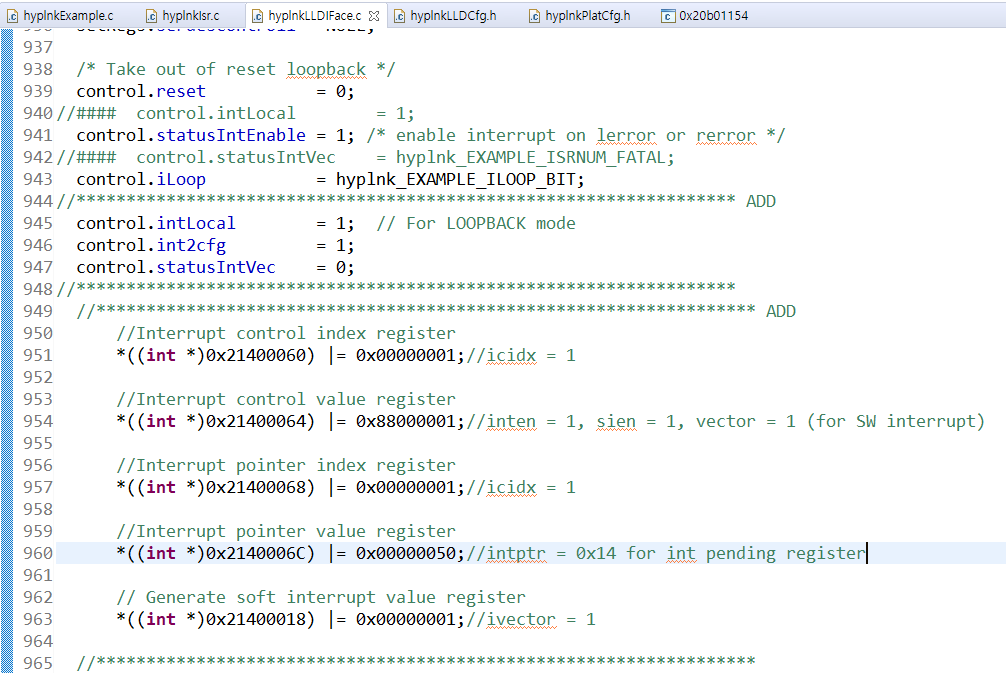

First, I removed the annotation. Then I do an experiment.

#define hypplnk_EXAMPLE_LOOPBACK

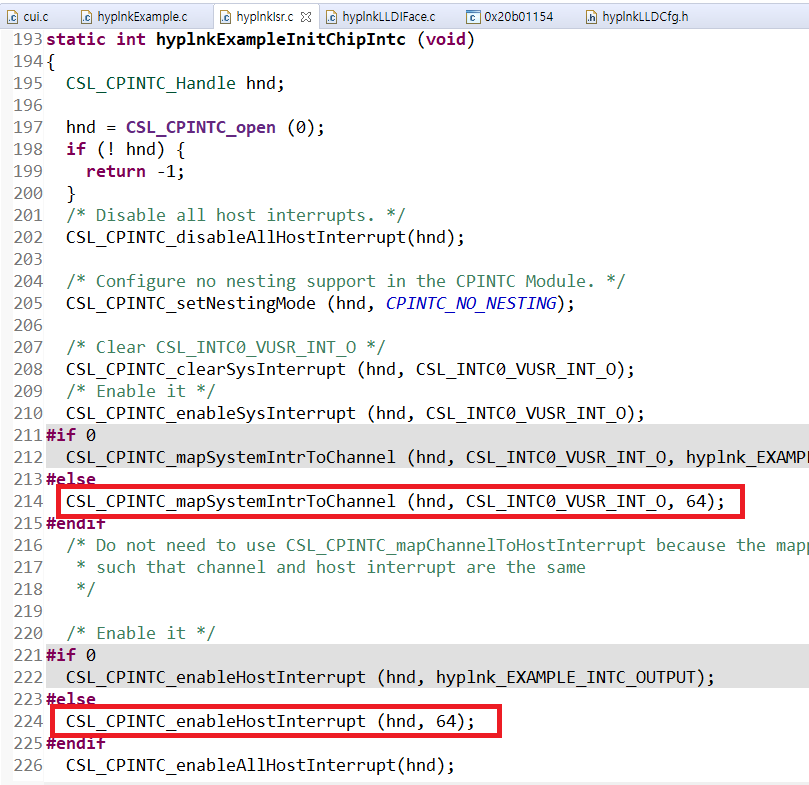

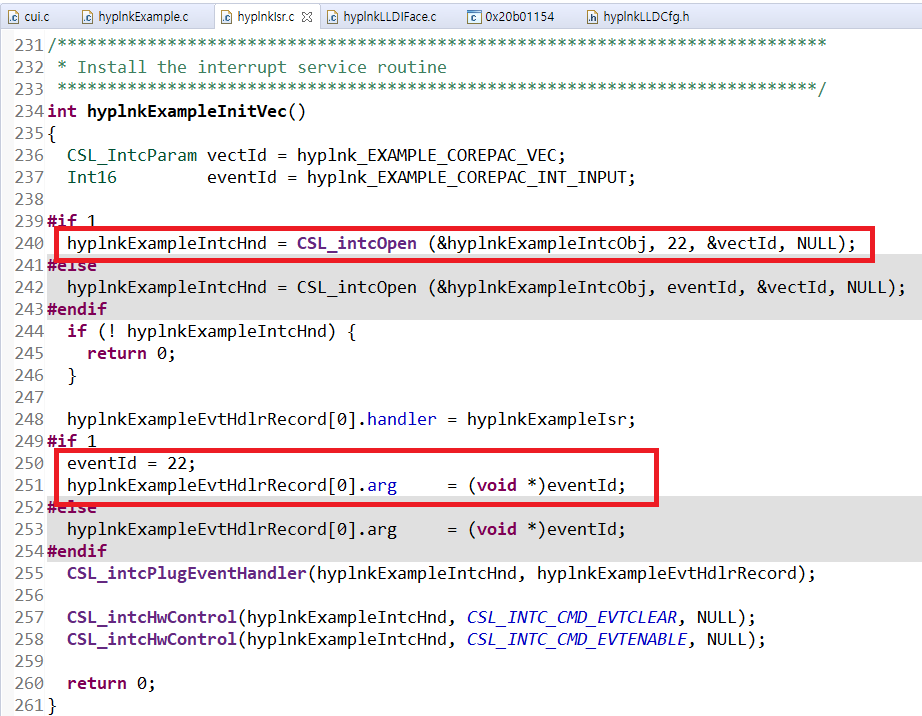

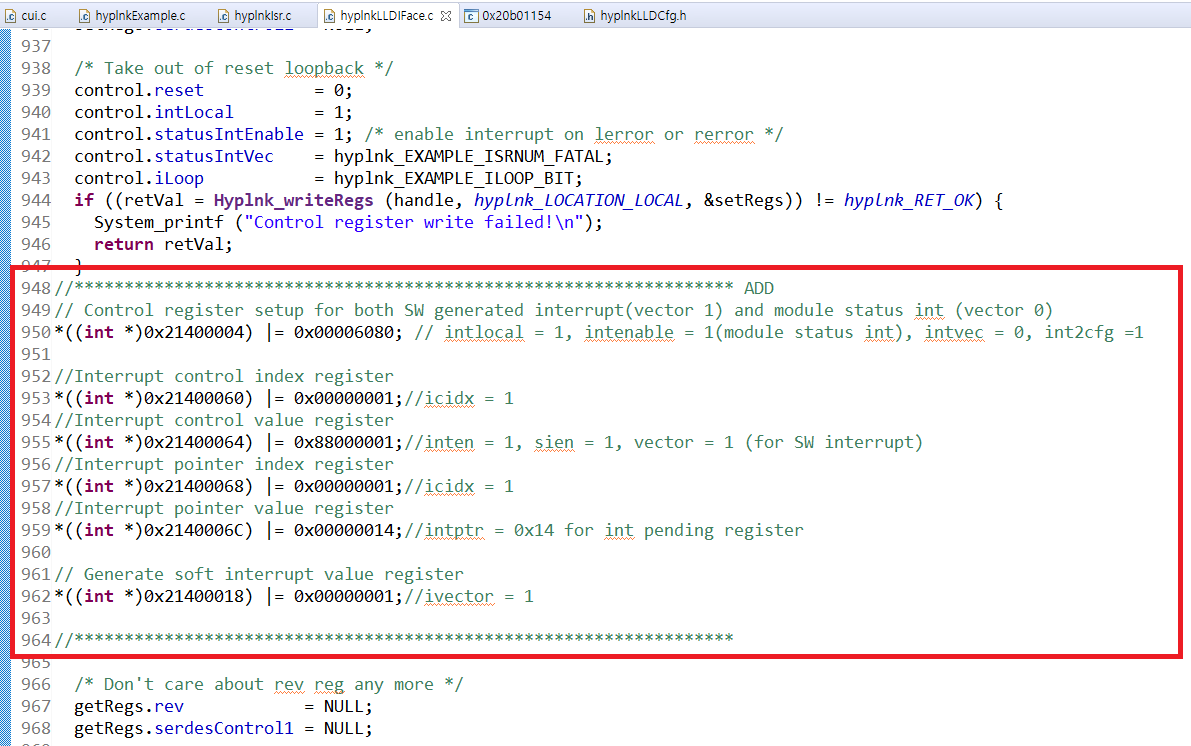

1) The ISR was initialized in the example project, but the ISR function was not executed. (void hypplnkExampleIsr (void *eventId)

- ISR not running in LOOPBACK mode?

- ISR running in Two 6678 DSP?

2) When the void hypplnkExampleIsr (void *eventId) function is executed, the transmitted data must be read. However, there was no function within the function to read or process the transmitted data.

- How do I check the data sent each time an interrupt is run? ... dataBuffer?~ Read whenever the receiving ISR is executed.!?~

Test LOG data as see below

//####################################################################################################

[C66xx_0] Version #: 0x01000105; string HYPLNK LLD Revision: 01.00.01.05:Nov 19 2012:16:04:15

About to do system setup (PLL, PSC, and DDR)

Power domain is already enabled. You probably re-ran without device reset (which is OK)

Constructed SERDES configs: PLL=0x00000228; RX=0x0046c485; TX=0x000cc305

system setup worke

About to set up HyperLink Peripheral

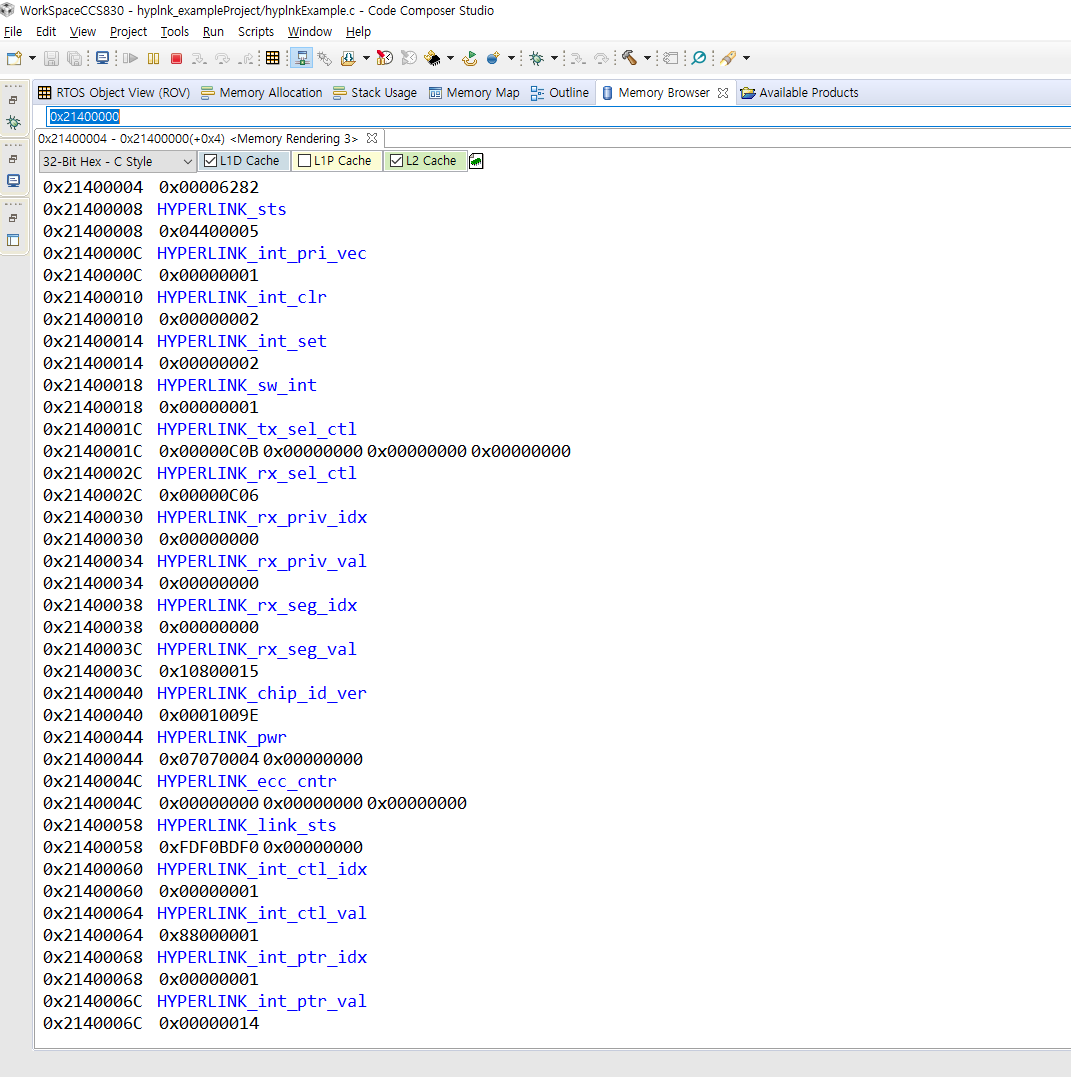

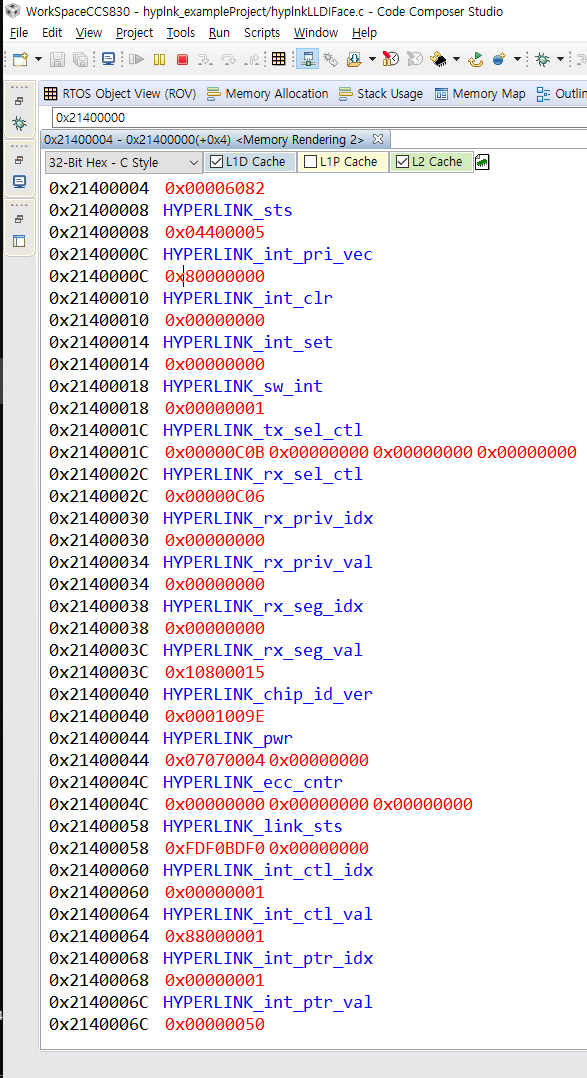

============== begin registers before initialization ===========

Revision register contents:

Raw = 0x4e901900

Status register contents:

Raw = 0x00002004

Link status register contents:

Raw = 0x00000000

Control register contents:

Raw = 0x00000001

Control register contents:

Raw = 0x00000000

============== end registers before initialization ===========

SERDES_STS (32 bits) contents: 0x00000001; lock = 1

============== begin registers after initialization ===========

Status register contents:

Raw = 0x04400005

Link status register contents:

Raw = 0xccf00cf0

Control register contents:

Raw = 0x00006202

============== end registers after initialization ===========

Waiting 5 seconds to check link stability

Precursors 0 Analysis: 1,0,1,0,0,1,0,0

Postcursors: 19 Analysis: 0,1,1,0,0,1,0,1

Link seems stable

About to try to read remote registers

============== begin REMOTE registers after initialization ===========

Status register contents:

Raw = 0x0440080f

Link status register contents:

Raw = 0xfdf0bdf0

Control register contents:

Raw = 0x00006202

============== end REMOTE registers after initialization ===========

Peripheral setup worked

About to read/write once

Single write test passed

About to pass 65536 tokens; iteration = 0

=== this is not an optimized example ===

Link Speed is 4 * 6.25 Gbps

Passed 65536 tokens round trip (read+write through hyplnk) in 16222 Mcycles

Approximately 247535 cycles per round-trip

=== this is not an optimized example ===

Checking statistics

About to pass 65536 tokens; iteration = 1

=== this is not an optimized example ===

Link Speed is 4 * 6.25 Gbps

Passed 65536 tokens round trip (read+write through hyplnk) in 16222 Mcycles

Approximately 247535 cycles per round-trip

=== this is not an optimized example ===

Checking statistics

About to pass 65536 tokens; iteration = 2

=== this is not an optimized example ===

Link Speed is 4 * 6.25 Gbps

Passed 65536 tokens round trip (read+write through hyplnk) in 16222 Mcycles

Approximately 247535 cycles per round-trip

=== this is not an optimized example ===

Checking statistics

About to pass 65536 tokens; iteration = 3

=== this is not an optimized example ===

Link Speed is 4 * 6.25 Gbps

Passed 65536 tokens round trip (read+write through hyplnk) in 16222 Mcycles

Approximately 247535 cycles per round-trip

//####################################################################################################

Thanks.